### Compilerconstructie

najaar 2012

http://www.liacs.nl/home/rvvliet/coco/

Rudy van Vliet kamer 124 Snellius, tel. 071-527 5777 rvvliet(at)liacs(dot)nl

college 7, dinsdag 5 november 2013

Storage Organization

Code Generation

## 7.1 Storage Organization

```

Free Memory

Static

Stack

Code

Неар

```

Typical subdivision of run-time memory into code and data areas

## 7.2 Stack Allocation of Space

```

void quicksort (int m, int n)

{ int i;

if (n > m)

main ()

{ readArray();

a[0] = -9999;

a[10] = 9999;

quicksort(1,9);

}

int a[11];

void readArray() /* Reads 9 integers into a[1],...a[9].

{ int i;

[/* Picks a separator value v, and partitions a[m.n] so that

[a[m.p-1] are less than v, a[p]=v, and a[p+1.n] are

equal to or greater than v. Returns p. */

if (n > m)

{ i = partition(m, n);

quicksort(m, i-1);

quicksort(i+1, n);

```

#### Possible **Activations**

```

leave quicksort(5,9)

leave quicksort(1,9)

leave main()

ter main()

enter readArray()

lawe readArray()

enter quicksort(1,9)

enter partition(1,9)

lawe partition(1,9)

enter quicksort(1,3)

leave quicksort(1,3)

enter quicksort(5,9)

```

ω

## Traversal of Activation Tree

- 1. Sequence of procedure  $\mathit{calls} \approx \mathit{preorder}$  traversal

- Sequence of procedure  $\textit{returns} \approx \text{postorder traversal}$

- 3. When control lies at particular node ( $\approx$  activation), the 'open' ( $\mathit{live}$ ) activations are on path from root

### 7.2.1 Activation Trees

## **Activation Records**

| Temporaries | Local data | Saved machine status | Access link | Control link | Returned values | Actual parameters |

|-------------|------------|----------------------|-------------|--------------|-----------------|-------------------|

Possible (order of) elements of activation record

# Code Generator Position in a Compiler

| program   | source       |

|-----------|--------------|

| End       | Front        |

| code      | intermediate |

| Optimizer | Code         |

| code      | intermediate |

| Generator | Code         |

| program   | target       |

- Output code must

- be correct

- use resources of target machine effectively

- Code generator must run efficiently

Generating optimal code is undecidable problem Heuristics are available

# 8.1 Issues in Design of Code Generator

- Input to the code generator

- The target program

- Instruction selection

- Register allocation and assignment

- Evaluation order

## Input to the Code Generator

- Intermediate representation of source program

- Three-address representations (e.g., quadruples)

- Virtual machine representations (e.g., bytecodes)

- Postfix notation

- Graphical representations (e.g., syntax trees and DAGs)

- $\bullet$  Information from symbol table to determine run-time addresses

- Input is free of errors

- Type checking and conversions have been done

10

### The Target Program

- Common target-machine architectures

- RISC: reduced instruction set computer

- CISC: complex instruction set computer

- Stack-based

- Possible output

- Absolute machine code (executable code)

- Relocatable machine code (object files for linker)

- Assembly-language

11

### **Instruction Selection**

- $\bullet$  Given IR program can be implemented by many different code sequences

- Different machine instruction speeds

- Naive approach: statement-by-statement translation, with a code template for each IR statement

Example: x = y + zID RO, y ADD RO, RO, z ST x, RO Now, a = b + cLD RO, b

ADD RO, RO, c

ST a, RO

LD RO, a

ADD RO, RO, e

ST d, RO d = a + e

12

# Instructions of Target Machine

Target Machine

Designing code generator requires understanding of target machine and its instruction set  $\begin{tabular}{ll} \end{tabular} \label{table_equation}$

Our machine model

byte-addressable

- $\bullet$  Load operations: LD dst, addr e.g., LD r, x or LD  $r_1, r_2$

Store operations: ST x, r

- $\bullet$  Computation operations: OP  $\textit{dst}, \textit{src}_1, \textit{src}_2$  e.g.,  $\textit{SUB}\ r_1, r_2, r_3$

- ullet Unconditional jumps: BR L

- $\bullet$  Conditional jumps: Bcond r,L e.g., BLTZ r,L

14

13

assumes operands are integers

has n general purpose registers RO,R1,...,Rn

# Addressing Modes of Target Machine

| Form  | Form Address              | Example         |

|-------|---------------------------|-----------------|

| r     | r                         | LD R1, R2       |

| x     | 8                         | LD R1, x        |

| a(r)  | a + contents(r)           | LD R1, a(R2)    |

| c(r)  | c + contents(r)           | LD R1, 100(R2)  |

| *7    | contents(r)               | LD R1, *R2      |

| *c(r) | contents(c + contents(r)) | LD R1, *100(R2) |

| #c    |                           | LD R1, #100     |

## Addressing Modes (Examples)

a[j] = cLD R1, i MUL R1, R1, #8 LD R2, a(R1) ST b, R2 LD R1, c LD R2, j MUL R2, R2, #8 ST a(R2), R1 = a[i]: if x < y goto L LD R1, x LD R2, y SUB R1, R1, R2 BLTZ R1, M LD R1, p LD R2, 0(R1) ST x, R2

16

15

### **Instruction Costs**

- Costs associated with compiling / running a program

Compilation time

Size, running time, power consumption of target program

- Finding optimal target problem: undecidable

- (Simple) cost per target-language instruction:  $-1 + cost \ for \ addressing \ modes \ of \ operands \\ \approx \ length \ (in \ words) \ of \ instruction$

#### Examples:

| Ē        | Ē   | Ē   | ins         |

|----------|-----|-----|-------------|

| R1,      | RO, | RO, | instruction |

| *100(R2) | ×   | R1  | tion        |

| N        | 2   | 1   | cost        |

|          |     |     |             |

17

# 8.4 Basic Blocks and Flow Graphs

- Basic block: instructions, such that maximal sequence of consecutive three-address

- (a) Flow of control can only enter through first instruction of

- Э Control leaves block without halting 9 branching

Flow graph: graph with nodes: basic blocks edges: indicate flow between blocks

18

#### **Determining Basic Blocks**

- Determine leaders

- First three-address instruction is leader

- Ŋ Any instruction that is target of goto is leader

- ω Any instruction that immediately follows goto is leader

- For each leader, its basic block consists of leader and instructions up to next leader (or end of program) 림

19

20

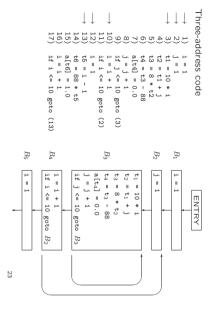

#### Determining Basic **Blocks** (Example)

#### Determine leaders

for i=1 to 10 do for j=1 to 10 do a[i,j]=0.0;for i=1 to 10 do a[i,i]=1.0;Pseudo code Three-address code j = 1 t1 = 10 \* i t2 = t1 + j t3 = 8 \* t2 t4 = t5 - 86 a[t4] = 0.0 j = j + 1 if j <= 10 goto j = 1 - 1 t6 = x - 1 t6 = x + t5 a[t6] 88 \* t5 a[t6] 88 \* t5 a[t6] 88 \* t5 (13) 2 (3)

#### Determining Basic **Blocks** (Example)

#### Determine leaders

Pseudo code

Three-

code

for i = 1 to 10 do for j = 1 to 10 do a[i,j] = 0.0; for i = 1 to 10 do a[i,i] = 1.0;

7,65,43210987654321

$\downarrow \downarrow \downarrow$ j = 1 t1 = 10 \* i t2 = t1 0 \* i t2 = t + t2 t3 = 8 \* t + t2 t4 = t3 - 88 a[t4] = 0.0 j = j + 1 if i <= 10 goto i = 1 1 t5 = i - 1 t6 = 88 \* t5 a[t6] = 1.0 goto 2

(3)

(13)

21

#### Flow Graph

Edge from block  ${\cal B}$  to block  ${\cal C}$

- of Cif there is (un)conditional jump from end of  $\boldsymbol{B}$  to beginning

- $\mathsf{if}\ C$ and B does immediately follows  ${\it B}$  in original order, not end in unconditional jump

22

#### Flow Graph (Example)

### Loops in Flow Graph

Loop is set of nodes

- $\bullet \ \, \text{With unique loop entry } e \\ \bullet \ \, \text{Every node in } L \ \, \text{has}$

- Example nonempty path in L to e

- $\{B_3\}$ , with loop entry  $\{B_2, B_3, B_4\}$ , with I

loop

$B_3$

entry  $B_2$  •  $\{B_6\}$ , with loop entry  $B_6$

$B_4$  $B_3$  $B_2$  $B_1$ t<sub>1</sub> = 10 \* i t<sub>2</sub> = t<sub>1</sub> + j t<sub>3</sub> = 8 \* t<sub>2</sub> t<sub>4</sub> = t<sub>3</sub> - 88 a[t<sub>4</sub>] = 0.0 j = j + 1 if j <= 10 goto if i î + ENTRY 10 goto B<sub>2</sub>  $B_3$

$B_5$ p. 24

### **Next-Use Information**

- Next-use information is needed for dead-code elimination and register assignment

- (i) x = a \* b

- $(j) \quad z = c + x$

Instruction j uses value of x computed at i x is live at i, i.e., we need value of x later

For each three-address statement x=y op z in block, record next-uses of x,y,z

25

# **Determining Next-Use Information**

For single basic block

- Assume all non-temporary variables are live on exit

- Make backward scan of instructions in block

- $\bullet$  For each instruction  $i:\ x=y\ \textit{op}\ z$

- 1. Attach to  $\emph{i}$  current next-use- and liveness information of

- 2. Set x to 'not live' and 'no next use'

- 3. Set y and z to 'live' Set 'next uses' of y and z to i

26

# **Passing Liveness Information over Blocks**

Example of loop

27

# **Passing Liveness Information over Blocks**

Example of loop

28

### Compiler constructie

college 7 Storage Organization Code Generation

Chapters for reading: 7.1, 7.2–7.2.3 8.intro, 8.1, 8.2, 8.4

29