## System-Level Design Methodology for Streaming Multi-Processor Embedded Systems

Hristo N. Nikolov

# System-Level Design Methodology for Streaming Multi-Processor Embedded Systems

#### **PROEFSCHRIFT**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van de Rector Magnificus prof. mr. P.F. van der Heijden, volgens besluit van het College voor Promoties te verdedigen op donderdag, 16 April 2009 te klokke 16.15 uur

door

Hristo N. Nikolov geboren te Gabrovo, Bulgaria in 1974 Samenstelling promotiecommissie:

promotor Prof.dr.ir. Ed F. Deprettere co-promotor Dr.ir. Todor Stefanov

overige leden: Prof.dr. Daniel Gajski (University of California, Irvine, USA)

Prof.dr. Rainer Leupers (Aachen University of Technology, Germany)

Prof.dr.ir. Angel Popov (Technical University of Sofia, Bulgaria)

Prof.dr. Henk Corporaal (Technical University Eindhoven)

Prof.dr. Henk Corporaal Prof.dr. Joost Kok Prof.dr. Harry Wijshoff Prof.dr. Frans Peters

The work in this thesis was carried out in the Artemisia project supported by PROGRESS/STW.

System-Level Design Methodology for Streaming Multi-Processor Embedded Systems Hristo Nikolov Nikolov. -

Thesis Universiteit Leiden. - With ref. - With summary in Dutch

ISBN 978-90-9024163-0

Copyright © 2009 by Hristo Nikolov Nikolov, Leiden, The Netherlands.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in the Netherlands

To my daughters Michaela and Anetta; To my wife Boyanka for all the support and understanding...

### Contents

| A | cknow | ledgme                 | ents                                                            | xi |  |  |  |

|---|-------|------------------------|-----------------------------------------------------------------|----|--|--|--|

| 1 | Intr  | troduction             |                                                                 |    |  |  |  |

|   | 1.1   | 1 Problem statement    |                                                                 |    |  |  |  |

|   | 1.2   | Solution approach      |                                                                 |    |  |  |  |

|   |       | 1.2.1                  | Platform-based design at system level                           | 8  |  |  |  |

|   |       | 1.2.2                  | Kahn Process Network model of computation                       | 11 |  |  |  |

|   | 1.3   | Scope                  | of Work                                                         | 12 |  |  |  |

|   | 1.4   | Resear                 | rch Contributions                                               | 14 |  |  |  |

|   | 1.5   | Related Work           |                                                                 |    |  |  |  |

|   | 1.6   | 5 Dissertation Outline |                                                                 |    |  |  |  |

| 2 | Eml   | oedded                 | System-level Platform synthesis and Application Mapping – ESPAM | 25 |  |  |  |

|   | 2.1   | The M                  | ultiprocessor Platform                                          | 26 |  |  |  |

|   |       | 2.1.1                  | Multiprocessor memory architecture                              | 26 |  |  |  |

|   |       | 2.1.2                  | Data communication and synchronization mechanism                | 27 |  |  |  |

|   |       | 2.1.3                  | Platform interconnect protocol                                  | 27 |  |  |  |

|   |       | 2.1.4                  | Implementation details                                          | 28 |  |  |  |

|   |       | 2.1.5                  | System-level platform model                                     | 32 |  |  |  |

|   | 2.2   | Autom                  | nated MPSoC Synthesis                                           | 33 |  |  |  |

|   |       | 2.2.1                  | Platform specification                                          | 34 |  |  |  |

|      | Cantanta |

|------|----------|

| VIII | Contents |

|   | 3.2<br>3.3<br>3.4 | Applyid 3.3.1 3.3.2 3.3.3 3.3.4 3.3.5                          | Buffer sizes and system performance  Dataflow feed-back loops  for MANY-TO-ONE mapping generation  ing the mapping rules  Polyhedral process networks (PPN)  Isolated average throughput of a PPN process  Process throughput in case of dataflow loops  Data rate of the streams in a PPN  Computing buffer sizes of the FIFO channels in PPNs  assion | 70<br>71<br>74<br>75<br>80<br>81<br>82<br>83<br>85<br>86<br>90 |  |  |

|---|-------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

|   |                   | 3.1.4<br>Rules 1<br>Applyi<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | Dataflow feed-back loops  for MANY-TO-ONE mapping generation  ing the mapping rules                                                                                                                                                                                                                                                                     | 71<br>74<br>75<br>80<br>81<br>82<br>83                         |  |  |

|   |                   | 3.1.4<br>Rules 1<br>Applyi<br>3.3.1<br>3.3.2<br>3.3.3          | Dataflow feed-back loops  for MANY-TO-ONE mapping generation  ing the mapping rules                                                                                                                                                                                                                                                                     | 71<br>74<br>75<br>80<br>81<br>82<br>83                         |  |  |

|   |                   | 3.1.4<br>Rules 1<br>Applyi<br>3.3.1<br>3.3.2                   | Dataflow feed-back loops  for MANY-TO-ONE mapping generation  ing the mapping rules  Polyhedral process networks (PPN)  Isolated average throughput of a PPN process                                                                                                                                                                                    | 71<br>74<br>75<br>80<br>81<br>82                               |  |  |

|   |                   | 3.1.4<br>Rules 1<br>Applyi<br>3.3.1                            | Dataflow feed-back loops                                                                                                                                                                                                                                                                                                                                | 71<br>74<br>75<br>80<br>81                                     |  |  |

|   |                   | 3.1.4<br>Rules t                                               | Dataflow feed-back loops                                                                                                                                                                                                                                                                                                                                | 71<br>74<br>75<br>80                                           |  |  |

|   |                   | 3.1.4<br>Rules t                                               | Dataflow feed-back loops                                                                                                                                                                                                                                                                                                                                | 71<br>74<br>75                                                 |  |  |

|   | 3.2               | 3.1.4                                                          | Dataflow feed-back loops                                                                                                                                                                                                                                                                                                                                | 71<br>74                                                       |  |  |

|   |                   |                                                                | • •                                                                                                                                                                                                                                                                                                                                                     | 71                                                             |  |  |

|   |                   | 3.1.3                                                          | Buffer sizes and system performance                                                                                                                                                                                                                                                                                                                     |                                                                |  |  |

|   |                   |                                                                |                                                                                                                                                                                                                                                                                                                                                         | 70                                                             |  |  |

|   |                   | 3.1.2                                                          | Throughput in case of merged processes                                                                                                                                                                                                                                                                                                                  | 70                                                             |  |  |

|   |                   | 3.1.1                                                          | Process throughput and system performance                                                                                                                                                                                                                                                                                                               | 69                                                             |  |  |

|   | 3.1               | System                                                         | n performance                                                                                                                                                                                                                                                                                                                                           | 66                                                             |  |  |

| 3 | Tech              | niques                                                         | for Narrowing the Design Space                                                                                                                                                                                                                                                                                                                          | 63                                                             |  |  |

|   | 2.6               | Conclu                                                         | isions                                                                                                                                                                                                                                                                                                                                                  | 61                                                             |  |  |

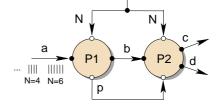

|   |                   | 2.5.4                                                          | Respecting the conditions                                                                                                                                                                                                                                                                                                                               | 59                                                             |  |  |

|   |                   | 2.5.3                                                          | Preserving the consistency of our PNs with dynamic parameters                                                                                                                                                                                                                                                                                           | 59                                                             |  |  |

|   |                   | 2.5.2                                                          | Process network instance                                                                                                                                                                                                                                                                                                                                | 58                                                             |  |  |

|   |                   | 2.5.1                                                          | Motivating example                                                                                                                                                                                                                                                                                                                                      | 57                                                             |  |  |

|   | 2.5               | Discus                                                         | sion                                                                                                                                                                                                                                                                                                                                                    | 56                                                             |  |  |

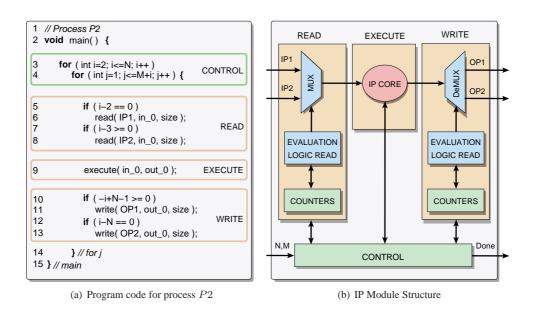

|   |                   | 2.4.3                                                          | IP core types and interfaces                                                                                                                                                                                                                                                                                                                            | 56                                                             |  |  |

|   |                   | 2.4.2                                                          | IP Module – basic idea and structure                                                                                                                                                                                                                                                                                                                    | 53                                                             |  |  |

|   |                   | 2.4.1                                                          | Uniform structure of a KPN process                                                                                                                                                                                                                                                                                                                      | 52                                                             |  |  |

|   | 2.4               | 4 Dedicated IP core integration with ESPAM                     |                                                                                                                                                                                                                                                                                                                                                         |                                                                |  |  |

|   |                   | 2.3.3                                                          | Code generation: SW code for processors                                                                                                                                                                                                                                                                                                                 | 47                                                             |  |  |

|   |                   | 2.3.2                                                          | Automated programming – input specification                                                                                                                                                                                                                                                                                                             | 46                                                             |  |  |

|   |                   | 2.3.1                                                          | Automated Derivation of Process Networks                                                                                                                                                                                                                                                                                                                | 44                                                             |  |  |

|   | 2.3               | Automated Programming of MPSoCs                                |                                                                                                                                                                                                                                                                                                                                                         |                                                                |  |  |

|   |                   | 2.2.2                                                          | Platform synthesis                                                                                                                                                                                                                                                                                                                                      | 35                                                             |  |  |

|   |                   | 222                                                            |                                                                                                                                                                                                                                                                                                                                                         |                                                                |  |  |

4 Case studies

| ix |

|----|

|    |

|     | 4.1                  | Experimental setup                          |                                                     |     |  |  |

|-----|----------------------|---------------------------------------------|-----------------------------------------------------|-----|--|--|

|     | 4.2                  | 4.2 Homogeneous MPSoCs design with DAEDALUS |                                                     |     |  |  |

|     |                      | 4.2.1                                       | Design time                                         | 93  |  |  |

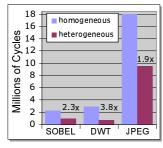

|     |                      | 4.2.2                                       | Performance results and accuracy of the DSE numbers | 94  |  |  |

|     |                      | 4.2.3                                       | Synthesis results                                   | 96  |  |  |

|     |                      | 4.2.4                                       | Conclusions                                         | 96  |  |  |

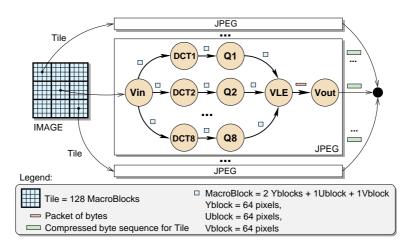

|     | 4.3                  | Hetero                                      | geneous MPSoCs design with DAEDALUS                 | 97  |  |  |

|     |                      | 4.3.1                                       | Design time                                         | 97  |  |  |

|     |                      | 4.3.2                                       | Performance results                                 | 98  |  |  |

|     |                      | 4.3.3                                       | Synthesis results                                   | 99  |  |  |

|     |                      | 4.3.4                                       | Conclusions                                         | 99  |  |  |

|     | 4.4                  | Putting                                     | g DAEDALUS to work                                  | 100 |  |  |

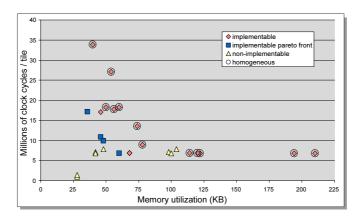

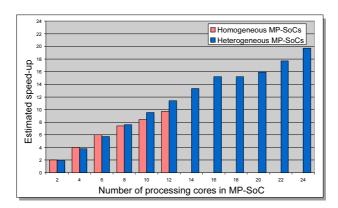

|     |                      | 4.4.1                                       | Simulation-level DSE                                | 101 |  |  |

|     |                      | 4.4.2                                       | Implementation-level DSE                            | 104 |  |  |

|     |                      | 4.4.3                                       | Conclusions                                         | 107 |  |  |

| 5   | Sum                  | mary a                                      | nd Conclusions                                      | 109 |  |  |

| Bib | liogr                | aphy                                        |                                                     | 113 |  |  |

| San | nenv                 | atting                                      |                                                     | 119 |  |  |

| Cui | durriculum Vitae 121 |                                             |                                                     |     |  |  |

### Acknowledgments

It is my privilege and great pleasure to convey my gratitude to those who have, directly or indirectly, supported me and helped me during the PhD study.

First, I would like to thank all the people I have worked with in Bulgaria and who have played a role in building my knowledge, my experience and expertise. I am grateful to my teachers for all the things I have learned from them and, in particular, to my mentors during the master project I had at TU-Sofia for showing me the way to the scientific research, and especially, for encouraging me to continue and to do a PhD. Also, I am thankful to all my colleagues and friends at Innovative MicroSystems Ltd. and Fabless Ltd. who contributed to the successful start of my engineering career. Many thanks for the great, enthusiastic atmosphere. Working for these companies complemented the background of knowledge I have obtained at the University with industrial experience related to systems-on-chip design and digital design for FPGAs. Now when I write these words, I realize how much the scientific and engineering background I have built while studying and working in Bulgaria helped me during the PhD research.

The work presented in this dissertation has been supported by PROGRESS, the embedded systems and software research program of the Dutch Technology Foundation STW, under the project ARTEMISIA (Project number LES 6389). I would like to acknowledge PROGRESS and STW for financially supporting my research and the dissemination of the achieved results at various scientific forums worldwide. In particular, special acknowledments go to all people involved in the administration of the ARTEMISIA project.

This dissertation is the result of work conducted at the Leiden Institute of Advanced Computer Science (LIACS), Leiden University, in collaboration with researchers from University of Amsterdam and Delft University of Technology. For the successful collaboration, I express my gratitude to all the people with whom I worked in the context of the ARTEMISIA project and with whom I had very interesting discussions, both scientific and non-scientific. I would like also to acknowledge the people from TU/e with whom I had interesting discussions at several joint projects meetings organized by PROGRESS.

xii Acknowledgments

I am glad to say that I enjoyed the time of the PhD study in our group at LIACS. It was a research path that, although it was not easy, led to fruitful results. Moreover, the conducted research enriched my knowledge and expertise in multiprocessor systems-on-chip and design automation for embedded multi-processor systems. It was pleasure working together with my colleagues and my supervisor prof. Ed Deprettere. In addition, I want to thank our former secretary Gonnie for helping me to settle in The Netherlands.

Many thanks to all my friends who know how much I appreciate our friendship. I am pleased to note that for the past several years, it turned out that the two thousands kilometers between Bulgaria and The Netherlands are nothing for real friendship and "every time we meet as we have never separated", as a friend of mine says. Also, I am lucky that some of my friends are close to me, here in The Netherlands. Hereby, I express my special gratitude to them for always giving me a helping hand when needed! In addition, I would like to thank my close relatives and my family, especially my mother and my brother, for believing in me and for their lifetime support.

Finally, with my deepest love I express my gratitude to Boyanka, my wife, for her love and trust; For sacrificing her professional career in Bulgaria and following me in this PhD adventure.

Hristo N. Nikolov March, 2009 Leiden, The Netherlands

|         | 1 |  |  |  |

|---------|---|--|--|--|

| Chapter |   |  |  |  |

In a paper published in April 1965 [1], Gordon Moore discussed the future of electronics. Among his predictions for integrated circuits was that the number of circuit components fabricated on a single silicon chip would double every each year, reaching 65000 by 1975<sup>1</sup>. Moore's prediction fit the facts so well that people began referring to it as Moore's Law. It is still known as Moore's Law, even when Moore altered his projection to a doubling every two years in 1975. Since then, the spectacular rate of progress in semiconductor technology has made possible dramatic advances in computers and has led to the emerging of the embedded (electronic) Systems-on-Chip (SoC) concept<sup>2</sup>, which in turn have significantly altered almost all areas of human endeavor. In particular, the embedded systems have become the electronic engines of modern consumer and industrial devices, from automobiles to satellites, from washing machines to high-definition TVs, from cellular phones to complete base stations.

Through the years, the increasingly demanding complexity of applications have significantly expanded the scope and the complexity of these SoCs, i.e., the more available resources provided by every new generation of technology have been used to implement more and more sophisticated and diverse system features. Currently, for modern embedded systems in the realm of high-throughput multimedia, imaging, and signal processing, the complexity of embedded applications has reached a point where the performance requirements of these applications can no longer be supported by embedded systems based on a single processing component. Thus, the emerging embedded SoC platforms are increasingly becoming multiprocessor platforms (MPSoCs) encompassing a variety of hardware (HW) and software (SW) components. The ever increasing requirements imply also that, for efficiency and performance, in an MPSoC different application tasks have to be executed by different types of processing components which are optimized for the execution of particular tasks. It is a common knowledge that higher performance is achieved by a dedicated (customized and optimized) HW IP core because it works more efficiently than programmable processors.

<sup>&</sup>lt;sup>1</sup> At that time, no chips had been manufactured with more than 60 components.

<sup>&</sup>lt;sup>2</sup> Embedded systems are application domain specific information processing systems that are tightly coupled to their environment.

Evidently, highest efficiency and performance is achieved by MPSoCs consisting of only dedicated IP cores. However, dedicated IPs lack flexibility in making design modifications, a feature playing an important role in the time-to-market competition. Therefore, most of to-day's MPSoCs are heterogeneous in nature, i.e., a constellation of programmable processors and dedicated IPs, delivering high flexibility and high performance at the same time.

The long design cycle and the ever increasing time-to-market pressure impose clear requirements for systematic and, moreover, automated design methodologies for building heterogeneous MPSoCs. In such methodologies, the intrinsic computational power is not only used effectively and efficiently, but also the time and effort to design a system containing both hardware (HW) and software (SW) remains acceptable. Although embedded systems have been designed for decades, the systematic design of such systems with well defined methodologies, automation tools and technologies has gained attention primarily in the last 10-15 years. For example, a well adopted approach to deal with the embedded SoC design complexity is the Top-Down methodology which allows the designers to manage design complexity at different (hierarchical) levels of implementation details. Currently, this approach is successfully used together with the hardware/software (HW/SW) co-design methodology where HW and SW are designed (almost) independently and concurrently. This allows hardware and software integration testing during the early stages of design resulting in reduced number of design cycles, and consequently, in reduced overall design time. Nowadays end, applying the Top-Down and the HW/SW co-design methodologies with the support of electronic design automation (EDA) tools, is the most efficient design philosophy offering benefits such as reduced design time, design reuse, flexibility in making design changes, faster exploration of alternative architectures, and increased productivity.

Unfortunately, most of the current methodologies for multiprocessor system design are still based on descriptions at register transfer level (RTL) of design abstraction created by hand using, for example, VHDL or C. Such methodologies were effective in the past when SoC platforms based only on a single processor or processor-coprocessor architectures were considered. However, applications and platforms used in many of today's new system designs are mainly based on heterogeneous multiprocessor platforms. As a consequence, the designs are so complex that traditional design practices are now inadequate, because creating RTL descriptions of complex MPSoCs is error-prone and time-consuming even by using the Top-Down methodology. In addition, the complexity of high-end, computationally intensive applications in the multimedia domain further exacerbates the difficulties associated with the traditional hand-coded RTL design and HW/SW co-design methodologies. To execute an application on a MPSoC, the system has to be programmed, which is performed in several steps. First, the application is partitioned into tasks. Second, tasks are assigned (mapped on) to processors (programmable and/or non programmable). Finally, based on the mapping, the MPSoC is programmed, which requires writing program code for each of the programmable processors using languages such as C/C++. The program code includes code implementing the tasks' behavior and code for synchronization the data movement between the tasks (processing components, respectively). In recent years, a lot of attention has been paid to the building of MPSoCs. However, insufficient attention has been paid to the development of concepts, methodologies, and tools for efficient programming of such systems, so that the programming still remains a major difficulty and challenge [2]. Today, system designers experience difficulties in programming MPSoCs because the way an application is specified by 1.1 Problem statement 3

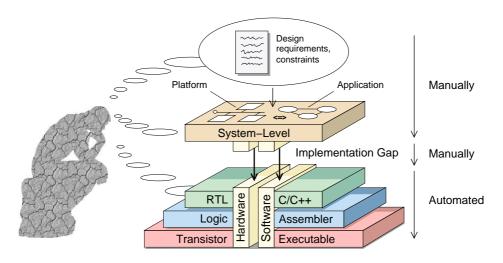

Figure 1.1: The Implementation Gap.

an application developer, typically as a sequential program, does not match the way multiprocessor systems operate, i.e., multiprocessor systems contain processing components that run in parallel.

#### 1.1 Problem statement

For all the reasons stated above, we conclude that:

1) The use of an RTL specification as a starting point for multiprocessor system design methodologies is a bottleneck. Although the RTL specification has the advantage that the state of the art synthesis tools can use it as an input to automatically implement an MPSoC, we believe that a multiprocessor system should be specified at a higher level of abstraction. This is the only way to solve the problems caused by the low level (detailed) RTL specification. The concept of system-level design of embedded systems, which raises the abstraction level of the design process above RTL to cope with design complexity, has been around for several years already and has shown a lot of potential. Despite of this, system-level design of (heterogeneous) MPSoCs still involves a substantial number of challenging design tasks. For example, MPSoCs need to be modeled and simulated to study system behavior in order to evaluate a variety of different design options. Once a good candidate has been found, it needs to be implemented, which involves the synthesis of its architectural components. However, moving up from the detailed RTL specification to a more abstract system-level specification opens (typically a large) gap between the deployed system-level specifications and actual physical implementations. We call it implementation gap which is illustrated in Figure 1.1. Indeed, on the one hand, the RTL specification is very detailed and close to an implementation, thereby allowing an automated synthesis path from RTL specification to implementation. This is obvious if we consider the current commercial synthesis tools where the RTL-to-netlist synthesis is very well developed and efficient. On the other hand, the com-

plexity of today's embedded systems forces us to move to higher levels of abstraction when designing a system, but currently, there exists no mature methodologies, techniques, and tools to move down from the high-level system specification to an implementation. Therefore, the implementation gap has to be closed by devising a systematic and automated way to convert a system-level specification effectively and efficiently to an RTL specification.

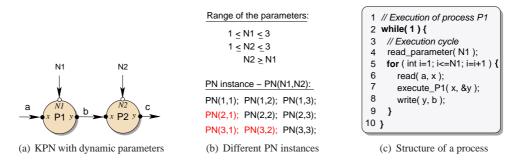

2) Programming multiprocessor systems is a tedious, error-prone, and time consuming process. On the one hand, the applications are typically specified by application developers as sequential programs using imperative programming languages such as C/C++ or Matlab. Specifying an application as a sequential program is relatively easy and convenient for application developers. However, the sequential nature of such specification does not reveal the available concurrency in an application because only a single thread of control is considered. Also, memory is global and all data resides in the same memory source. On the other hand, system designers need parallel application specifications, because when an application is specified using a parallel model of computation (MoC)<sup>3</sup>, the programming of multiprocessor systems could be done in a systematic and automated way. This is so because the multiprocessor platforms contain processing components that run in parallel, and a parallel MoC represents an application as a composition of concurrent tasks with a well defined mechanism for inter-task communication and synchronization.

The facts discussed above suggest that to program an MPSoC, system designers have to partition an application into concurrent tasks starting from a sequential program (delivered by application developers) as a reference specification. Then, they have to assign the application tasks to different processors<sup>4</sup> and to write specific program code for each programmable processor. Partitioning of an application into tasks consumes a lot of time and effort because the system designers have to study the application in order to identify possible task- and/or datalevel parallelism that is available, and to reveal it. Moreover, an explicit synchronization for data communication between the application tasks is needed. This information is not available in the sequential program and has to be specified by the designers explicitly. Therefore, an approach and tool support are needed for application partitioning and code generation, i.e., (C/C++) code for each processor of an MPSoC, to allow systematic and automated programming of MPSoCs. Currently, for a wide range of processors, the path from C/C++ to final executable code is fully automated.

In this dissertation, we address the issues of design, program, and implementation of MPSoCs in a specific way which allows us to devise a particular solution of closing the implementation gap. A motivation and an overview of the solution is presented in the next section.

#### 1.2 Solution approach

In this section, we give an overview of the solution approach we propose in order to close the implementation gap described in Section 1.1. The ideal approach would be a tool (or set of tools) that could automatically identify a set of application tasks and map them onto a multiprocessor platform guaranteeing the correct functionality and timing with optimal re-

<sup>&</sup>lt;sup>3</sup> A model of computation is the definition of the set of allowable operations used in computation.

<sup>&</sup>lt;sup>4</sup> This step may also involves SW/HW partitioning decisions.

source utilization. This tool should take a design description at the pure functional level together with performance and other constraints, and considering a target platform, it should produce optimized implementation. The ideal situation is not fulfilled (yet) for the general case, however, in this dissertation we present our methodology in which the issues of automated design, programming, and implementation of MPSoCs are addressed in a particular way, focusing on a particular application domain. Based on its characteristics, we make some assumptions (see section "Scope of work") which enabled the development of techniques to close the implementation gap.

As we mentioned already, the state of the art Top-Down and HW/SW co-design methodologies have been a topic of interest for years, but the proposed methodologies lack productivity and effectiveness when targeting MPSoCs design. In addition, these methodologies fail in raising the level of abstraction above RTL. Therefore, a new *design philosophy* is needed to address the aforementioned design challenges. At the same time, we believe that this new design philosophy must exploit the great potential and the advantages of the Top-Down and HW/SW co-design methodologies (see Section 1) that they offer for single-processor systems design.

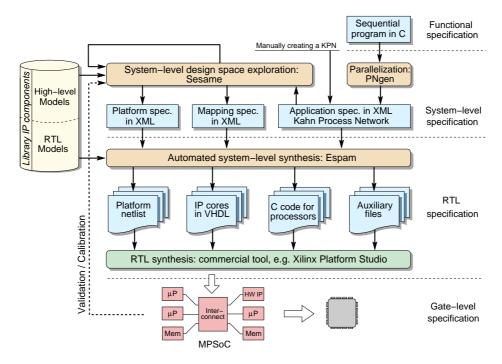

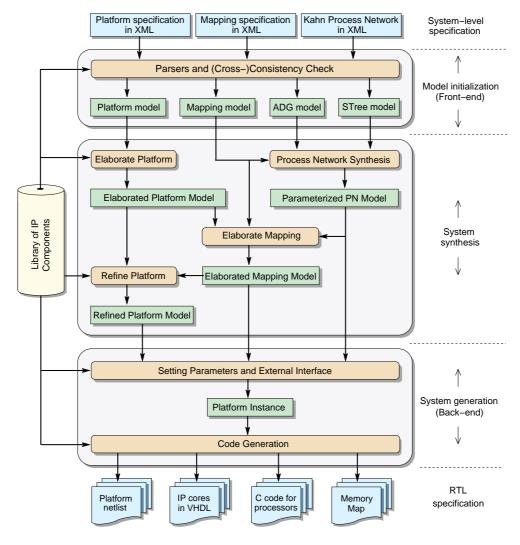

In this dissertation we propose a methodology, implemented in a tool-flow called DAEDALUS [3,4], for automated design, programming, and implementation of MPSoCs starting at a high level of abstraction. The methodology is built on the concept of Platform-Based Design (PBD) [5] being a promising new approach to master the ever growing complexity of today's embedded systems. The main idea is starting from a functional specification of an application and a description of an MPSoC at system level, to refine and translate them to lower RTL descriptions in a systematic and automated way. The proposed methodology is illustrated in Figure 1.2. It starts with an application written as a sequential C program which represents the required system behavior at functional level. In DAEDALUS, there are specifications at three additional levels of abstraction, namely at SYSTEM-LEVEL, RTL-LEVEL, and GATE-LEVEL.

#### **Definition 1.2.1 (System level)**

System level is a level of abstraction above RTL including both hardware and software.

The SYSTEM-LEVEL specification in DAEDALUS consists of three parts written in XML format:

- 1. *Application Specification*, describing an application in a parallel form as a set of communicating application tasks.

- 2. *Platform Specification*, describing the topology of a multiprocessor platform. The type of platforms we consider is presented in Section 2.1.5.

- 3. *Mapping Specification*, describing the relation between all application tasks in *Application Specification* and all components in *Platform Specification*.

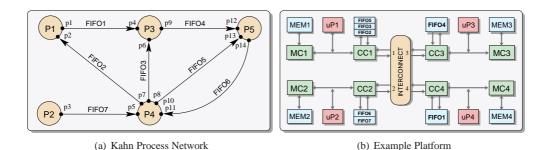

The application specification captures the initial application in a parallel form. For this purpose, we use the Kahn Process Network (KPN) [6] model of computation, i.e., a network of concurrent processes communicating via FIFO channels. For applications specified as

Figure 1.2: DAEDALUS System Design Flow.

parameterized static affine nested loop programs in C (a class of programs discussed in Section 2.3.1), KPN descriptions can be derived automatically by using the PNGEN tool [7], see the top right part in Figure 1.2. In case the application does not fit in this class of programs, the application specification needs to be derived by hand. The platform and the mapping specifications can be created manually or can be generated automatically. Specifying a multiprocessor platform by hand is a simple task that can be performed in a few minutes, because the high-level platform specification does not contain any details about the MPSoC components and, e.g., their physical interfaces. Describing a mapping in XML format is even simpler than writing a platform specification.

The components in the platform specification are taken from a library of IP components, see the left part of Figure 1.2. The library consists of predefined generic parameterized components which constitute the platform model in the DAEDALUS design flow. The platform model is a key component in the proposed solution approach because it allows alternative MPSoCs to be easily built by instantiating components, connecting them, and setting their parameters in an automated way. The components in the library are represented at two levels of abstraction: High-level models are used for constructing and modeling multiprocessor platforms at system level. Low-level models of the components are used in the translation of the multiprocessor platforms to RTL, ready for final implementation.

The platform and the mapping specifications can be generated automatically as a result of a design space exploration. For this purpose, we use the SESAME tool [8] (see the top of

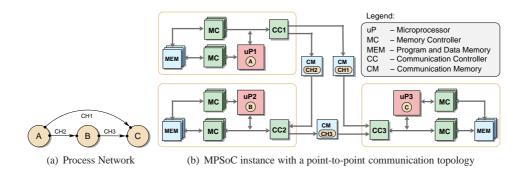

Figure 1.2) developed at the University of Amsterdam. As input, SESAME uses the KPN application specification and the high-level models of the components from our library. The output is a set of pairs, i.e., a platform specification and a mapping specification, each pair representing an optimal mapping of the initial application onto a particular MPSoC in terms of performance and given certain constraints.

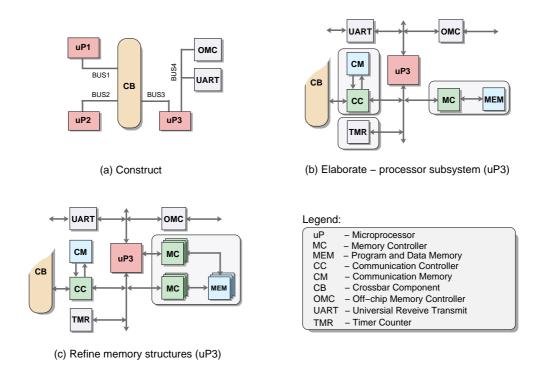

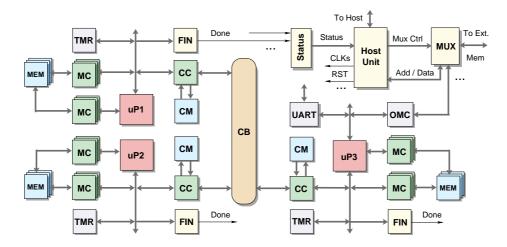

The SYSTEM-LEVEL specification of an MPSoC is systematically and automatically translated to RTL-LEVEL in several steps. In the beginning, the platform specification is used to construct a platform instance. The platform instance is an abstract model of an MPSoC because, at this stage, no information about the target physical platform is taken into account. The model defines only the key system components of the platform and their attributes. Then, the abstract platform model is refined to an elaborate (detailed) parameterized RTL model which is ready for an implementation on a target physical platform. The refined system components are instantiated by setting their parameters based on the target physical platform features. Finally, program code for each programmable processor in the multiprocessor platform is generated in accordance with the application and mapping specifications. The described System-Level to RTL-Level translation is performed by the Espam tool [9], see Figure 1.2. Details about the platform model and Espam are given in Chapter 2.

As output, ESPAM delivers a hardware (synthesizable VHDL code) description of an MP-SoC and software (C/C++) code to program each processor in the MPSoC. The hardware description, namely a RTL-LEVEL specification of a multiprocessor system, is a model that can adequately abstract and exploit the key features of a target physical platform at the register transfer level of abstraction. It consists of two parts: 1) Platform topology, a netlist description defining in greater detail the MPSoC topology; 2) Hardware descriptions of IP cores, containing predefined and custom IP cores (processors, memories, etc.) used in Platform topology selected from Library IP Cores. Also, it generates custom IP cores needed as a glue/interface logic between components in the MPSoC. ESPAM converts the XML application specification to efficient C/C++ code including code implementing the functional behavior together with code for synchronization of the communication between the processors. This synchronization code contains a memory map of the MPSoC, and read/write synchronization primitives. The generated program C/C++ code for each processor in the MPSoC is given to a standard GCC compiler to generate executable code.

A commercial synthesizer can convert the generated hardware RTL-LEVEL specification to a GATE-LEVEL specification, thereby generating the target platform gate-level netlist, see the bottom part of Figure 1.2. This GATE-LEVEL specification is actually the system implementation. The current version of ESPAM facilitates automated multiprocessor platform synthesis and programming targeting Xilinx FPGA technology, and thus, we use development tools (a GCC compiler and a VHDL synthesizer) provided by Xilinx [10] to generate the final bit-stream file that configures a specific FPGA. We use the FPGA platform technology for prototyping purpose, however, the generated FPGA MPSoC implementations may also be the final system implementation if, e.g., certain system requirements are met. In addition, the results we obtain from prototyping are used for validation/calibration of the high-level models in order to improve accuracy of the design space exploration process. The techniques in the ESPAM tool are flexible enough to target other physical platform technologies.

With DAEDALUS, we propose a model-driven design methodology and below we highlight its key characteristics:

- To address the challenges associated with the programming of MPSoCs presented in Section 1.1, in the proposed design methodology we use a parallel model of computation, namely the Kahn Process Network (KPN) MoC [6], to represent an application as a set of (concurrent) application tasks. These tasks are further mapped onto programmable (ISA) and non-programmable (dedicated IPs) processing components of an MPSoC. Exploiting the KPN MoC, we propose techniques for programming the ISA processors in an automated way.

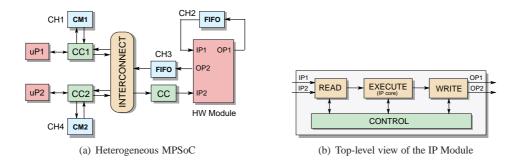

- DAEDALUS facilitates design of heterogeneous systems where both programmable and non-programmable processors are used as processing components. In case of non-programmable processing components, we propose an approach for automated integration of predefined (third-party) dedicated IP cores. An IP core can be created by hand or it can be generated automatically from C descriptions using high-level synthesis tools like, e.g., the PICO tool from Synfora [11]. High-level (behavioral) synthesis is out of the scope of this dissertation and the DAEDALUS system design methodology.

- To facilitate automated implementation of MPSoCs, we have identified a platform model which captures very well the operational semantics of the KPN MoC. This allows system-level platform descriptions to be refined and translated to detailed RTL descriptions in an automated way. The good match between the KPN MoC and our platform model results in efficient implementations when KPNs are executed on such platforms;

- Our PBD methodology starts with application, platform, and mapping specifications

at system level. By applying our techniques, the system-level models are translated

to HW platform descriptions at RTL, and SW code executed on the processors of the

platform. From RTL to final implementation, DAEDALUS utilizes state of the art (commercial) synthesis and compiler tools;

- By using the proposed application and platform models, a design space exploration at system level is enabled. It allows evaluating the performance of different application to platform mappings and alternative HW/SW partitionings. Such exploration result in a number of promising system design candidates, each defined by an application, a platform, and a mapping specification.

The PBD concept and the KPN MoC are motivated in the following sections. Our platform model is discussed in detail further in this dissertation.

#### 1.2.1 Platform-based design at system level

The concept of a platform encapsulates the notion of reuse, facilitating the adaptation of a common design to a variety of different (domain specific) applications [5, 12]. The platform-based design at system level is a powerful approach that has the potential of addressing the

MPSoC design challenges, in both HW and SW design, in a unified way. We chose PBD because this approach:

- Includes both hardware and embedded-software design;

- Favors the use of high levels of abstraction for the initial design specification;

- Facilitates effective design exploration;

- Achieves detailed implementation by refinement.

The principles of PBD in our approach consist of starting at the highest level of abstraction, i.e., System-level in Figure 1.1, which includes application and platform specification, hiding unnecessary details of an implementation. In PBD, important parameters of the implementation are summarized in an abstract model(s) and design space exploration is limited to a set of available components, i.e., the IP library in Figure 1.2. Furthermore, the design is carried out as a sequence of refinement steps that go from the initial specification towards the final implementation using platforms at various levels of abstraction.

Below, we give definitions associated with the PBD approach of our design methodology presented in this dissertation.

#### **Definition 1.2.2 (Platform)**

The platform is a *library of components* that can be assembled to generate a design. The library contains *processing* blocks that carry out the appropriate computation and also *communication* blocks and *memory* blocks that are used to interconnect the processing blocks.

#### **Definition 1.2.3 (Platform model)**

The platform model includes the library of components, and defines the way the components can be assembled assuming particular (inter-component) communication and synchronization mechanisms.

#### **Definition 1.2.4 (Platform instance)**

A platform instance is a set of components that is selected from the the platform and whose parameters are set. The components in a platform instance are connected in accordance with the platform model.

#### **Definition 1.2.5 (Platform instance refinement)**

Refinement is a process of adding (implementation) details to the original platform instance.

The refined platform instance does not necessarily represent a final implementation, however, it is closer than the original platform instance since it contains more details about the target implementation.

#### **Definition 1.2.6 (Mapping)**

In the proposed methodology, mapping is an assignment of application tasks to processing components of a platform instance.

The notion of a platform is associated with a set of potential solutions to a design problem where each platform instance implements a design point, i.e., a particular solution. Therefore, we need to capture the process of mapping functionality, i.e., what the system is supposed to do, to platform computational, communication, and memory components that will be used to build a platform instance. This process is an essential step for refinement, which provides a mechanism to proceed towards implementation by closing the implementation gap in a structured way. In addition, taking into account the MPSoC design challenges, we advocate that in order to allow systematic and automated system design where the fundamental steps of functional partitioning, allocation of computational resources, integration, and verification are supported,

- 1. Applications have to be specified in some parallel model of computation (MoC), at a high level of abstraction;

- 2. Platform instances have to be specified in a parameterized abstract form (a platform model);

- 3. Methods have to be provided to map the former onto the latter.

A well known principle in designing complex systems is the *separation of concerns*, initially introduced by Edsger Dijkstra in his essay from 1974 "On the role of scientific thought" [13]. Separation of concerns is one of the key principles in software engineering and object oriented programming. However, it is an important principle in PBD as well [14]. The main goal is to design systems so that different kinds of concerns are identified and separated (optimized independently) in order to cope with complexity, and to achieve the required quality factors such as robustness, adaptability, maintainability, and reusability. The principle can be applied in various ways. For instance, in PBD, it is important to keep communication and computation components well separated as different methods are usually needed and used to represent and to refine these components. Communication plays a fundamental role in determining the properties of models of computation. Subsequently, special care is needed in defining the communication mechanism of a platform model since it may help or hinder design/components reuse and performance.

Based on the foregoing discussion, we state that the PBD at system level is an attractive candidate to form the basis for new design methodologies. Moreover, if linked to the Top-Down and HW/SW co-design methodologies at RTL, it results in a synergy that can be very productive. In our case, we create this link by closing the implementation gap. In addition, the main goals of reduced design time, design re-use, flexibility in making design changes, faster exploration of alternative platform instances and mappings, and increased productivity, can not be achieved without tools supporting this new design methodology. Therefore, in our approach we are equally interested in developing techniques for:

- Raising the design abstraction to system level by utilizing the platform-based design concept to deal with design complexity;

- Automated translation of the system-level models to RTL descriptions, therefore, closing the implementation gap in a systematic and automated way.

#### 1.2.2 Kahn Process Network model of computation

As discussed in Section 1.1, programming multiprocessor systems is a tedious, error-prone, time consuming process and we argued that in order to facilitate an automated programming, a parallel MoC is required for application representation.

#### But what should this MoC be?

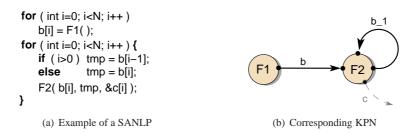

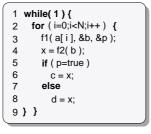

Many parallel MoCs exist [15], and each of them has its own specific characteristics. Evidently, to make the right choice of a parallel MoC, we need to take into account the application domain we target. In this dissertation, we consider only data-flow dominated applications in the realm of multimedia, imaging, and signal processing that naturally contain tasks communicating via streams of data. Such applications are very well modeled by using the parallel data-flow MoC called Kahn Process Network (KPN) [6, 16].

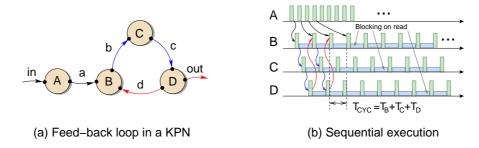

Gilles Kahn defined a formal model for networks of concurrent processes that communicate through unbounded First-In First-Out (FIFO) channels carrying streams of data tokens [6, 16]. Processes produce tokens and send them along a communication channel where they are stored until the destination process consumes them. Communication channels are the only method processes may use to exchange information. For each channel there is a single process that produces tokens and a single process that consumes tokens. Multiple producers or multiple consumers connected to the same channel are not allowed. Kahn requires the execution of a process to be suspended when it attempts to get data from an empty input channel. At any given point, a process is either enabled or it is blocked waiting for data on only one of its input channels. When enabled, a process may access only one channel at a time and when blocked on a channel, a process may not access other channels.

Kahn showed that requiring processes to block when attempting to read from empty channels allows processes to be represented as continuous functions over a complete partial order (the set of streams of data elements with a prefix order). A program graph can be represented as a collection of equations that have a unique minimum solution that corresponds to the history of all tokens produced on all streams. Thus, systems that obey Kahn's model are determinate: the history of tokens produced on the communication channels is uniquely determined by the equations representing the program graph and does not depend on the execution order [6]. This implies that as long as blocking reads are enforced, the results of a computation are unique and correct whether the processes are executed sequentially, concurrently, or in parallel. The number of tokens produced, and their values, are determined by the definition of the system and not by the scheduling of operations. However, the number of data elements that must be buffered on the communication channels during execution does depend on the execution order and is not completely determined by the KPN definition.

Because process networks expose parallelism and make communication explicit, they are well suited for targeting MPSoC implementations of a variety of signal processing and scientific computation applications such as embedded signal and image processing. Many researchers [8,17–21] have already indicated that KPNs are suitable for efficient mapping onto multiprocessor platforms. In addition, we motivate our choice of using the KPN MoC by observing that the following characteristics of a KPN can take advantage of the parallel resources available in multiprocessor platforms:

The KPN model is determinate: Irrespective of the schedule chosen to evaluate the

network, the same input/output relation always exists. This gives a lot of scheduling

freedom that can be exploited when mapping process networks onto multi-processor

architectures;

- Distributed Control: The control is completely distributed to the individual processes

and there is no global scheduler present. As a consequence, distributing a KPN for

execution on a number of processing components is a simple task;

- Distributed Memory: The exchange of data is distributed over FIFO channels. There

is no notion of a global memory that has to be accessed by multiple processes (processors). Therefore, resource contention is greatly reduced if systems with distributed

memory are considered;

- Simple synchronization: The synchronization between the processes in a KPN is done by a blocking read mechanism on FIFO channels. Such synchronization can be realized easily and efficiently in both hardware and software.

#### 1.3 Scope of Work

In this section, we outline the assumptions and restrictions regarding the work presented in this dissertation. Most of them are discussed in further detail, where appropriate, throughout the dissertation.

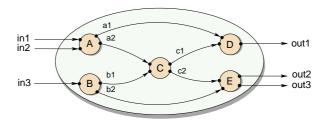

#### **Applications**

One of the main assumptions is that we consider only data-flow dominated applications in the realm of multimedia, imaging, and signal processing, that naturally contain tasks communicating via streams of data. The streams can represent any type of information, such as audio samples, image blocks, or video frames. Typically, the streams have one source and one sink, and must be non-lossy. Usually, reordering of data items (tokens) in streams is not acceptable. The transformations that are performed on data streams can be quite complex and their granularity is design-dependent. These transformations may consume data from any number of streams and produce data to any number of streams. Such applications are very well modeled by using the KPN data-flow model of computation [6]. We consider KPNs that are input-output equivalent to static affine nested loop programs. The properties of such programs are discussed in Section 2.3.1. We are interested in this subset of KPNs because they are analyzable at design time, e.g., FIFO buffer sizes and execution schedules are decidable. Moreover, such KPNs can be derived automatically from the corresponding sequential programs [7, 22–24].

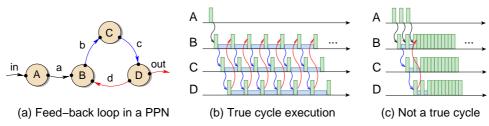

#### Application and platform models

The KPN choice as an application model is very important since it influences the platform model and the work/techniques presented in this dissertation. KPNs assume unbounded communication buffers. Writing is always possible and thus a process blocks only on reading from an empty FIFO. In the physical implementation, however, the communication buffers have bounded sizes, and therefore, a blocking write synchronization mechanism is used as well. The problem of deciding whether a general Kahn Process Network can be scheduled with bounded memory is undecidable [25, 26]. However, in our case this is possible because the process networks are derived by using the PNGEN tool from static affine nested loop programs (SANLPs), which programs require finite amount of memory to execute. In SANLPs, loop bounds, variable indexing functions, and condition expressions are all affine functions<sup>5</sup> of loop iterators and (static) parameters. This enables such programs to be modeled in terms of polyhedral domains, i.e., to represent a KPN, we use polyhedral descriptions. Therefore, the process networks we consider in this dissertation are actually polyhedral process networks (PPNs)<sup>6</sup>, being a subset of the Kahn process networks. In addition, we compute buffer sizes of the FIFO channels (see Section 3.3.5) such that a deadlock-free execution of the considered KPNs on our platform instances is guaranteed. The scheduling of process networks using bounded memory has been discussed in [25, 27]. Also, a number of tools and libraries have been developed for executing KPNs [28, 29]. In contrast to these approaches, the platform model we propose and use to construct (multiprocessor) platform instances does not require scheduling and run-time deadlock detection and resolution. Instead, the processing components in our platform model are self-scheduled following the KPN operational semantics using a blocking read/write synchronization mechanism, i.e., the KPNs are self-scheduled when executed on the MPSoCs. The main objective in devising the platform model was to allow building of MPSoCs which execute KPNs efficiently. In the proposed approach, we do not target particular processing components design rather than integrating such (taken from an IP library) in MPSoCs. Therefore, the main goal in order to achieve efficient KPN execution, is to enable efficient data communication between the processing components, i.e., a communication with minimum communication overhead. We achieved this by taking the main characteristics of the KPN MoC (see Section 1.2.2) into account when devising the platform model.

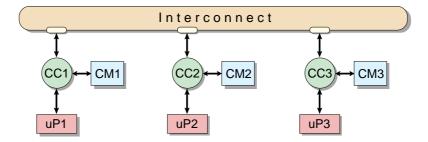

#### Multiprocessor platform instances – MPSoCs topology and execution model

With respect to the proposed application and platform models, we consider MPSoCs in which the processing components, i.e, programmable processors and/or HW IP cores, communicate data only through distributed memory units. Each memory unit can be organized as one or several FIFOs. The data communication among the processing components is realized by blocking read and write implemented in software and hardware. Such MPSoCs match and support very well the KPN operational semantics, thereby achieving high performance when KPNs are executed. If the number of processing components in a platform instance is less

<sup>&</sup>lt;sup>5</sup> Affine functions represent vector-valued functions of the form:  $f(x_1,...,x_n)=A_1x_1+...+A_nx_n+b$ .

<sup>&</sup>lt;sup>6</sup> For brevity, in this dissertation, we keep the notation 'KPN' because both, the PPNs and the KPNs, obey the same semantics. Some details about PPNs are given in Section 2.3.1 and Section 3.3.1.

than the number of processes of a KPN, then some of the programmable processors execute more than one process. These processes are scheduled at compile time and the generated program code for a given processor does not require/utilize an operating system. In our approach, we do not consider (high-level, behavioral) synthesis of HW IP cores. Instead, we propose an automated integration of predefined (third-party) HW IPs into (heterogeneous) MPSoCs. We do not impose restrictions on how the IP cores are created, i.e., by hand or by employing high-level design tools. In order an IP core to be added to the components library, however, an IP core has to implement the computation of only a single KPN process. We do not support sharing of an IP core between several KPN processes, i.e., more than one KPN processes to be implemented by a single dedicated IP. Additional requirements for the considered IP cores and their interfaces are discussed in Section 2.4.3. The programmable processors and the HW IP cores in our platforms can be connected in crossbar, point-to-point, or shared bus communication topologies. Details are given in Section 2.1.5.

#### **Tool inputs**

The input to the PNGEN tool is an application written as a static affine nested loop program (SANLP) in C. SANLP is a sequential program with some restrictions, discussed in Section 2.3.1. These restrictions allow for automated derivation of KPNs from SANLPs as described in Section 2.3.1. The PNGEN tool partitions a SANLP into processes only at function boundaries, i.e., the programmer divides the SANLP into functions, thus guiding the granularity of the automatically derived processes. Many applications in the considered domain (see above) can be represented as SANLPs. The ESPAM tool accepts as an input three specifications: an application specification, a platform specification, and a mapping specification. The application specification is a KPN either derived by PNGEN or a manually created. The platform specification is restricted in the sense that it must contain only components taken from the library of predefined parameterized components. The library allows and ensures that many alternative (multiprocessor) platform instances can be constructed and all of them fall into the class of MPSoCs we consider (see above). The mapping specification gives the relation between processes and processing components. Based on this, ESPAM determines automatically the most efficient mapping of FIFO channels onto distributed memory units. The platform and the mapping specifications can be created manually or automatically generated by the SESAME tool as a result of a design space exploration.

#### 1.4 Research Contributions

The work presented in this dissertation focuses on the design, programming, and implementation of multiprocessor systems (MPSoCs) starting from high (system) level of abstraction. Below, we outline our main contributions:

#### Closing the implementation gap

In this dissertation, we present our methods and techniques [9] for systematic and automated multiprocessor system design, programming, and implementation. They bridge the gap between the *system-level* specification and the *RTL* specification in a particular way which we consider as the main contribution of the dissertation. These methods and techniques have been implemented in a tool called ESPAM (Embedded System-level Platform synthesis and Application Mapping). More specifically, with ESPAM a system designer can specify a multiprocessor platform instance at a high level of abstraction in a short amount of time, say a few minutes. Then, ESPAM refines this specification to a real implementation, i.e.,

- 1. Generates a synthesizable (RTL) HW description of the MPSoC and

- 2. Generates SW code for each processor,

in an automated way, thereby closing in a particular way the implementation gap mentioned earlier. This reduces the design and programming time from months to hours. As a consequence, an accurate exploration of the performance of alternative multiprocessor platform instances becomes feasible at implementation level in a few hours.

#### System-level platform model matching the KPN programming (application) model

Our methods and techniques to closing the implementation gap are based on the underlying programming model and system-level platform model we use. Recall that ESPAM targets data-flow dominated (streaming) applications for which we use the Kahn Process Network (KPN) [6] model of computation as a programming (application) model. By carefully exploiting and efficiently implementing the simple communication and synchronization features of a KPN (see Section 1.2.2), we have identified and developed a set of generic parameterized components which we call a platform [9]. The platform and the way its components can be connected and synchronized comprise our platform model. We consider the platform model an important contribution of this dissertation because the set of components allows system designers to specify (construct) fast and easily many alternative multiprocessor platform instances that are implemented and programmed by ESPAM. The approach we propose is general enough and allows for building heterogeneous MPSoCs, i.e., different types of programmable processors and dedicated (third-party) HW IP cores, connected together in different communication topologies. In addition, the good match between the KPN MoC and the platform model results in efficient implementations when KPNs are executed on the considered MPSoCs.

#### Computing minimum KPN FIFO sizes that guarantee maximum performance

The automated MPSoC design and programming is enabled by using the KPN MoC. However, deriving a KPN specification is a time consuming process and confirmation of this fact can be found in the many system-level design approaches that use the KPN model [28–36].

The KPN model has been widely studied in our group at Leiden Embedded Research Center (LERC)<sup>7</sup> for almost a decade. The work presented in [37] is the first approach, known in the literature, to derive a KPN specification from a static affine nested loop program (SANLP). Several years of research in this direction resulted in techniques implemented in the COMPAAN tool [22, 24] for automated translation of SANLPs written in Matlab to KPN specifications. Although these techniques are very advanced, they do not address the problem of what the buffer sizes of the communication FIFO channels should be. This is a very important problem because if the FIFO buffers are undersized, this leads to a deadlock in the KPN behavior.

Recently, we have developed techniques for *improved* derivation of KPNs [7] from applications specified as sequential C programs. These techniques, implemented in the PNGEN tool [7], allow for automated computation of efficient buffer sizes that guarantee deadlock-free execution of our KPNs. In addition, in this dissertation we present an approach to compute minimum buffer sizes that guarantee maximum performance when KPNs are executed onto the considered MPSoCs. This is another important contribution of this dissertation because we are interested in high-performance multiprocessor systems and with our approach, the highest (theoretical) performance is achievable with reduced memory requirements.

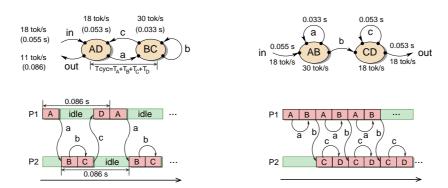

#### Systematic mapping of application tasks to processing cores

The decision of mapping application tasks to processing components is crucial in order to achieve high performance of the MPSoCs at reduced cost. Assuming that the data communication is efficient and does not introduce communication overhead, the maximum performance is achieved when every task is executed on a separate processor. However, this may introduce large resource overhead because due to task data dependences, most of the time processors may stay idle waiting for data. Therefore, the purpose of the mapping is to group tasks and assign them to processing components in a way that the number of processing components is minimized and the workload is balanced between the components without (or with reasonable) penalty in the overall performance.

Mapping application tasks to processors in an ad-hoc manner may lead to efficient implementations, however, it heavily depends on the expertise of the designer. In addition, for large design space, e.g., an application consisting of many application tasks and a platform that offer different types of processing components, the most efficient mapping can be easily overlooked. This motivated us to research techniques that aim at systematically mapping of application tasks to processing cores in an MPSoC. We devised an approach which exploits the properties of our application and platform models to narrow the design space in a systematic way. More precisely, we defined mapping rules used to create mappings that require fewer number of processing cores without compromising the achieved system performance. Moreover, the proposed approach can be effectively used to complement the techniques in the SESAME tool for reducing the design space that need to be traversed in the design space exploration process.

<sup>&</sup>lt;sup>7</sup> Leiden University, The Netherlands

1.5 Related Work 17

#### 1.5 Related Work

Systematic and automated application-to-platform mapping has been widely studied in the research community. The closest to our work is the SystemC-based design methodology presented in [38]. The proposed methodology consists of an automated design space exploration, performance evaluation, and automatic platform based system generation. But unlike DAEDALUS, [38] does not allow for automated parallelization of applications (it requires applications to be specified by hand in SystemC), nor design space exploration at application level. Similarly to our approach, the input for the design flow in [38] contains an executable application specification (written in SystemC), a target architecture template (in both approaches built from components taken from a component library) and mapping constraints of the SystemC modules (in our methodology we have a mapping giving a relation between the application and the architecture). In order to automate the design process, the SystemC application has to be written in a synthesizable subset of SystemC, called SysteMoC [39], whereas our restriction of the initial C program is to be a SANLP (see Section 2.3.1). The synthesizable subset of SystemC is required because for the IP core generation the authors use high-level synthesis tools, e.g., Mentor CatapultC or Forte Cynthesizer which is a major difference with our concept for heterogeneous MPSoCs design. Instead, in this dissertation we propose an approach for dedicated IP core integration based on an HW Module generation consisting of a wrapper around a predefined IP core.

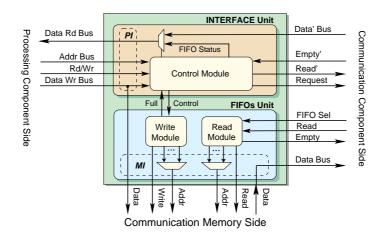

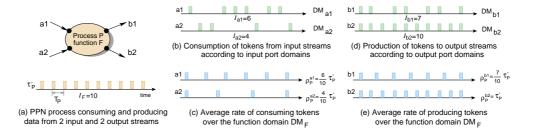

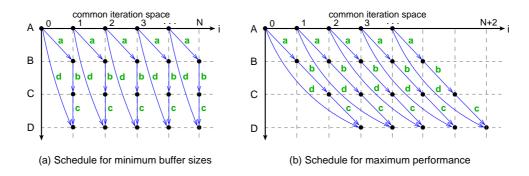

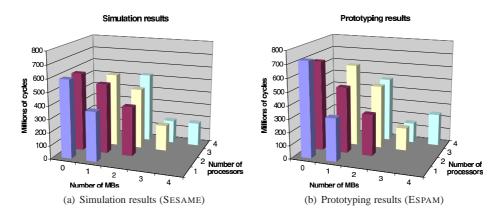

The Eclipse work [40] defines a scalable architecture template for designing stream-oriented multiprocessor SoCs using the KPN model of computation to specify and map data-dependent applications. The Eclipse template is slightly more general than the templates presented in this dissertation. However, the Eclipse work lacks an automated design and implementation flow. In contrast, our work provides such automation starting from a high-level system specification.