# Metamodeling and Code Generation in the Hardware/Software Interface Domain **32**

## Wolfgang Ecker and Johannes Schreiner

#### Abstract

In the HW/SW interface domain, specification of memory architecture and software-accessible hardware registers are both relevant for the implementation of hardware and the firmware running on it. Automated code generation of both HW and SW artifacts from a shared data source is a well-established method to ensure consistency. Metamodeling is a key technology to ease such code generation and to formalize the data structures target code is generated from. While this can be utilized for a wide range of automation and generation tasks, it is particularly useful for bridging the HW/SW design gap.

Metamodeling is the basis for the construction of large model-driven automation solutions that go far beyond simple code generation solutions. Based on the formalization metamodels provide, models can be incrementally transformed and combined to create more refined models for particular design tasks. IP-XACT and UML/SysML can be utilized within the scope of metamodeling. The utilization of these standards and the development of custom metamodels – targeted to specific design tasks – have proven to be highly successful and promise large potential for further productivity increase.

| Acronyms |                                   |

|----------|-----------------------------------|

| AHB      | Advanced High-performance Bus     |

| APB      | Advanced Peripheral Bus           |

| API      | Application Programming Interface |

| AST      | Abstract Syntax Tree              |

| AXI      | Advanced eXtensible Interface     |

| BNF      | Backus-Naur Form                  |

| CIM      | Computation Independent Model     |

W. Ecker (🖂) • J. Schreiner

Infineon Technologies AG, Neubiberg, Germany

e-mail: wolfgang.ecker@infineon.com; johannes.schreiner@infineon.com

<sup>©</sup> Springer Science+Business Media Dordrecht 2017

S. Ha, J. Teich (eds.), Handbook of Hardware/Software Codesign, DOI 10.1007/978-94-017-7267-9\_32

| CPU   | Central Processing Unit                           |  |  |  |  |  |  |

|-------|---------------------------------------------------|--|--|--|--|--|--|

| DMA   | Direct Memory Access                              |  |  |  |  |  |  |

| EBNF  | Extended Backus-Naur Form                         |  |  |  |  |  |  |

| EDA   | Electronic Design Automation                      |  |  |  |  |  |  |

| EMF   | Eclipse Modeling-Framework                        |  |  |  |  |  |  |

| GUI   | Graphical User Interface                          |  |  |  |  |  |  |

| HDL   | Hardware Description Language                     |  |  |  |  |  |  |

| HLS   | High-Level Synthesis                              |  |  |  |  |  |  |

| HTML  | Hypertext Markup Language                         |  |  |  |  |  |  |

| HW    | Hardware                                          |  |  |  |  |  |  |

| IEEE  | Institute of Electrical and Electronics Engineers |  |  |  |  |  |  |

| IP    | Intellectual Property                             |  |  |  |  |  |  |

| JSON  | JavaScript Object Notation                        |  |  |  |  |  |  |

| MDA   | Model-Driven Architecture                         |  |  |  |  |  |  |

| MoC   | Model of Computation                              |  |  |  |  |  |  |

| MOF   | Meta Object Facility                              |  |  |  |  |  |  |

| OCL   | Object Constraint Language                        |  |  |  |  |  |  |

| OMG   | Object Management Group                           |  |  |  |  |  |  |

| PIM   | Platform Independent Model                        |  |  |  |  |  |  |

| PSM   | Program State Machine                             |  |  |  |  |  |  |

| RTL   | Register Transfer Level                           |  |  |  |  |  |  |

| SoC   | System-on-Chip                                    |  |  |  |  |  |  |

| SPI   | Serial Peripheral Interface                       |  |  |  |  |  |  |

| SW    | Software                                          |  |  |  |  |  |  |

| TLM   | Transaction-Level Model                           |  |  |  |  |  |  |

| UML   | Unified Modeling Language                         |  |  |  |  |  |  |

| VHDL  | VHSIC Hardware Description Language               |  |  |  |  |  |  |

| VHSIC | Very High Speed Integrated Circuit                |  |  |  |  |  |  |

| XMI   | XML Metadata Interchange                          |  |  |  |  |  |  |

| XML   | Extensible Markup Language                        |  |  |  |  |  |  |

| XSD   | XML Schema                                        |  |  |  |  |  |  |

| XSLT  | Extensible Stylesheet Language Transformations    |  |  |  |  |  |  |

|       |                                                   |  |  |  |  |  |  |

## Contents

| 32.1 | Introdu                    | ction                              | 1053 |  |  |

|------|----------------------------|------------------------------------|------|--|--|

| 32.2 | What Is Metamodeling About |                                    |      |  |  |

|      | 32.2.1                     | A First Example                    | 1055 |  |  |

|      | 32.2.2                     | Terminology                        | 1061 |  |  |

|      | 32.2.3                     | History and Known Technologies     | 1064 |  |  |

|      | 32.2.4                     | The Case for Metamodeling          | 1065 |  |  |

| 32.3 | A Form                     | al Model of Metamodeling           | 1066 |  |  |

|      | 32.3.1                     | Basic Definitions                  | 1066 |  |  |

|      | 32.3.2                     | A Formal Representation of a Model | 1068 |  |  |

|      | 32.3.3                     | Metamodel Constraints on Models    | 1072 |  |  |

| 32.4  | 4 Metamodeling for HW/SW Codesign |      |  |  |  |  |

|-------|-----------------------------------|------|--|--|--|--|

|       | 32.4.1 Metamodeling Frameworks    | 1074 |  |  |  |  |

|       | 32.4.2 Related Standards          | 1082 |  |  |  |  |

| 32.5  | Generation                        | 1087 |  |  |  |  |

| 32.6  | Conclusion                        | 1089 |  |  |  |  |

| Refer | ences                             | 1089 |  |  |  |  |

## 32.1 Introduction

Productivity increases in the design of embedded systems always built on the idea of predesigning modules from smaller components, providing an abstract model and other views and packaging all that together for use in a higher-level design environment.

First, semi-custom design prepacked transistors to logic gates and provided models with logic functions, propagation delay, and a graphical representation symbolizing the functionality of the gate. Typical representatives for prepacked gates are AND gates with two, three, or four inputs and one output or a D flip-flop with clock, reset, and data (normally called D) input and one output (normally called Q). This packing also enabled the use of gates in a schematic editor which provides a graphical view of the model. This stage of development permitted increasingly complex designs which could no longer be manually handled on the lower levels of abstraction. The final layouts were therefore done by fully automatic place and route tools.

Next, gates were prepacked to RT components, associated with register-transfer functionality and with untimed or clock-related timing. The packing was enriched with schematic views, with operators or program constructs and their mapping to the RT components. A good example for this is an adder which supports various sized inputs and the associated information that a "+"-operator can be mapped to it. The essential achievement of this abstraction is that RTL synthesis tools can map RTL descriptions to gate-level netlists in an automated way.

Further pursuing this approach, IP components were introduced that were preimplemented in RTL and associated with more abstract TLM models to enable early and efficient simulations of multimillion – if not billion – transistor chips. Although that approach is now about 15 years old, this technique is not fully established. If established, generation of TLM and RTL top levels – i.e., abstract model and implementation – from a single source model is not a widely used approach. This is one of the main reasons for delayed introduction of automated IP-based design with TLM models: automation as provided by layout and RTL synthesis tools is not available. Further abstraction – except for some prepacked subsystems – is not widely used today [21].

Solely relying on the reuse of prepackaged items makes it very hard to implement innovative products since innovation is limited to novel combination of preimplemented items. To address this limitation, RTL synthesis provided an additional abstraction: the ability to describe the behavior of a design using sequential constructs known from programming languages following a specific coding style. By applying a mapping – called inference in the RTL domain – these sequential constructs are mapped to RTL netlists and RTL primitive components that are then further optimized and synthesized as described above. For example, an if-statement causes the insertion of multiplexers for all signals assigned in the statement blocks.

The increase of productivity in RTL-synthesis provided for a wide range of digital designs through behavioral constructs could however not be repeated. High-Level Synthesis (HLS) tools, state machine synthesizers, or processor generation tools – to name only some – could improve productivity only in very limited fields of application. Moreover, reuse and composition of IP components do not give the productivity increase that is often claimed since they help to design chips with a lot of transistors, yet the transistors still need plenty of custom firmware and software on top of them to work properly.

If a single tool cannot provide system-level automation – i.e., automation beyond implementation level – for a wide range of applications, why not use a tool suite with tools that follow the same concept, interact, and together provide a wide range of automation [8]. This approach is exemplified by Office suites which provide a collection of tools for presentations, text documents, spreadsheets, project management, and much more.

However, simple scripting as successfully used by many designers (see, e.g., [27]) is too expensive to provide a sufficient number of tools at an acceptable cost and effort. Metamodeling techniques [7] provide a substantial measure to dramatically shorten the building time of such tools. Therefore metamodeling is one key technology to enable system-level automation via tool suites and to ease the interaction between tools which are part of these tool suites.

The goal of this book section is to introduce metamodeling in general and to show how it helps to increase productivity around the HW/SW interface. In the first subsection, we introduce the general concept of metamodeling and show early metamodeling technologies. Afterward, we give a formal definition of a metamodel illustrating the formalization and giving an idea, on how metamodels can be used in a formalized design process. Finally, we describe some metamodeling techniques in use, show the idea of automatic view generation around the HW/SW interface, and illustrate the basic structure of a metamodeling framework.

#### 32.2 What Is Metamodeling About

First of all, metamodeling is different from other modeling approaches and also uses the term *model* differently than, e.g., in semi-custom or RTL design. This is further elaborated in Sect. 32.2.2. In metamodeling, a model describes an entity, mostly an intended design by its properties, its sub-entities, and the relationships between them.

## 32.2.1 A First Example

## 32.2.1.1 A Simplified View on the HW/SW Interface

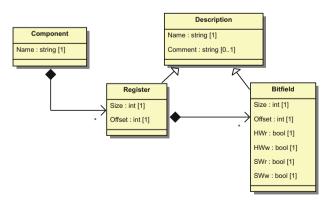

Figure 32.1 shows a very simple metamodel of an IP's register interface. Comparable register interfaces are a key component of generic HW/SW interfaces. The HW/SW interface works basically as follows:

- By writing a value to the base address of the IP plus an internal offset, a value is passed from software to hardware. From the SW point of view, this is similar to writing to a memory cell. Therefore, SW can treat those addresses as special variables. Additionally hardware can be attached to the register, e.g., to trigger actions when the register is accessed or when a specific value is written. Connection of the registers to the IP-HW is done via wires. IP-HW then processes the values of those wires.

- Storing a value in the bitfield from the hardware side or giving access to HW wires via the bitfield provides a way for the software to read a value from hardware. After having read the register the bitfield resides in, the software can further process the value. Similar to writing of values, SW handles the values read from the IP-HW like values from a memory. They can thus be treated like special variables in the software context.

In the following we focus on this basic mechanism, ignoring that there are additional possibilities for HW/SW interfaces such as CPU accessible special function registers, interrupts, or DMA request lines. When taking a closer look at the conceptual description above and considering the abstraction levels mentioned in the introduction, it becomes clear that several levels of abstraction with the same or different Model of Computation are bridged:

• The software side follows primarily a sequential, control flow-oriented execution order. The software is mostly developed in C and C++ – although assembler code

Fig. 32.1 Simple metamodel of register interfaces

is still used. These descriptions do not contain timing information and individual threads of execution have no degree of parallelism.

- The hardware side follows several concepts. Depending on the level of abstraction the hardware is observed from, it uses different modeling languages:

- When observed from the gate-level perspective, connected timed primitives mostly described in Verilog are used.

- On RTL, additional synchronous control flow or data flow is an appropriate view, typically modeled in VHDL or SystemVerilog.

- TLM communicating processes are mostly coded in SystemC.

## 32.2.1.2 A First Metamodel

Instead of trying to make one model composed of sub-models, each following an own model of computation and being interlinked with a multi-domain formalism as proposed in [12], metamodels follow another idea: metamodels identify involved entities and define their attributes and relations. Further, metamodels also define constraints such as types, valid values, or valid multiplicity.

Figure 32.1 shows the definitions for the key entities involved in a HW/SW interface: Component, Register, and Bitfield. Component is the root node. In this model, it has a required string attribute Name and an unlimited number of registers. The latter is shown by the association arrow and the multiplicity \*. Each Register has the mandatory attribute Offset, specifying the offset of the register in the address space of the component. Since a register must have this attribute, its multiplicity is set to 1. In addition, the offset must be a number which is defined by the type int of the attribute. Similarly, the register has a definition of its Size.

Finally, a register has one or more bitfields, again shown by the association arrow pointing at Bitfield and the multiplicity 1..\*. A Bitfield has an offset Offset in the bit space of the register and a Size. Their type is int since both must be an integer number. Both have multiplicity 1 since they are mandatory attributes for a bitfield. To specify how a bitfield can be accessed, our register meta-model has four mandatory Boolean attributes SWreadable, HWreadable, SWwritable, and HWwritable.

Figure 32.1 also shows two Unified Modeling Language (UML) generalization arrows. These arrows point from the entities Register and Bitfield to Description. They indicate that the entities Register and Bitfield acquire all attributes and associations from the arrow target Description. Since Description has the mandatory string attribute Name and the optional string attribute Comment, Register and Bitfield have these attributes too. Of course, Register and Bitfield acquire all properties of these attributes as well. Thus, inheritance does not provide additional measures to describe entities; however, it simplifies and structures the description of their properties.

If you noticed that Fig. 32.1 resembles a UML class diagram, you are right: Fig. 32.1 was captured with DoUML, an open-source UML editor [24]. Although metamodels and UML class diagrams have many things in common, they are not the same. As we will see later, metamodels are used in UML to define class diagrams.

#### 32.2.1.3 A First Model

With a metamodel at hand, a so-called *model* can be built that meets the constraints of the metamodel. In other words, legal instances of the metamodel can be built. The metamodeling technique follows the idea of separation of model and view, RTL models or SystemC-TLM models are thus called views in metamodeling terms. Before we discuss views in Sect. 32.2.1.4, we take a closer look at a model.

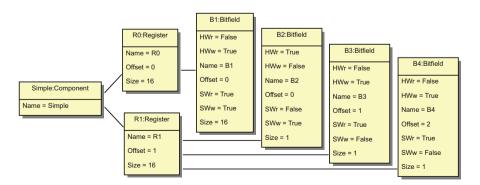

Figure 32.2 shows an example of a model specified in a graphical way using a UML object diagram. The model describes one instance of Component, its two registers R1 and R2 and its four bitfields B1 to B4. All Name attributes are set, i.e., the multiplicity constraints imposed from the metamodel are satisfied here. No Comment is set here which is legal since its multiplicity defined in the metamodel makes the attribute optional. All other mandatory attributes are set. The attributes Offset and Size are set to integer values, and HWr, HWw, SWr, and SWw are set to the Boolean values True or False.

There are further constraints originating from the semantics underlying the domain modeled here. These constraints are also met, which are easily comprehensible when looking at the diagrams. For example, every bitfield can either be read or written from each design domain, i.e., at least readable or the writable from software, as well as at least readable or writable from hardware. Further, the size of the bitfields is smaller than the size of the register. Since these additional constraints cannot be shown in a graphical way, they can be annotated in the tool capturing the metamodel either using a specific constraint language such as Object Constraint Language (OCL) (see [33]) or a programming language.

The model describes a component called Simple. This component has two 16bit registers R0 and R1. R0 is at the relative address 0 and R1 at the relative address 1. In contrast to what one might assume, the register does not describe a storage element in our model. Instead, it only describes an addressable shell. Bitfields are responsible for holding data and therefore the access rights are specified here. In our case, if a bitfield cannot be written from the SW side, the value intended to be written via the register access is simply ignored. If it cannot be read, then the value

Fig. 32.2 Simple model of a register interface

0 is returned. On the HW side, read and write access flags determine if there is a line from the register field to the HW core of the IP. The value written to HW is stored in a temporary register and the read value is directly taken from the IP core. These are all assumptions underlying our simplistic model. Industrial strength models such as IP-XACT (see Sect. 32.4.2.1) offer a wider range of possibilities here.

In addition to the UML diagram specification, models can be specified in many other ways, using, e.g., XML, JSON, or spreadsheets. It is important to assert that there is only one place where – and only one way how – the model is defined. This is called *single source* approach and prevents inconsistencies. It is especially important on the HW/SW interface since several design domains are bridged here.

#### 32.2.1.4 First Views

#### Documentation

For this model, several views exist in the design process. One of them is documentation. A tabular representation of such a documentation view is shown in Table 32.1. This view is used, e.g., by the verification engineers validating the interface, the software and hardware engineers making the interface, and by the customer developing software for the product the IP is integrated in. This table and all views shown here are simplified to provide a better perspective on the overall methodology. For an industrial documentation, please take a look, e.g., at [17].

#### RTL Code

A possible RTL view of our model is shown in Fig. 32.3. The bus interface is assumed to consist only of Addr, DataIn, DataOut, En, and Wr. En is "1" if the IP is accessed and Wr is "1" if a register should be written. Bus and register are assumed to have the same clock and reset signal and there is no pipelining or other delay on the bus. Of course, component metamodels such as the aforementioned IP-XACT have possibilities to define more sophisticated buses (e.g., AXI, AHB, or APB) which then lead to more complex bus interfaces. However, they follow the same basic concept that is introduced here.

The first process SW\_WRITE is responsible for write accesses from the SW side and the second process SW\_READ for read accesses. The first process is also responsible for the inference of the synchronous memory elements needed for

| Compo    | nent : $S$ | imple |            |        |      |       |       |       |       |

|----------|------------|-------|------------|--------|------|-------|-------|-------|-------|

| Register |            |       | Bitfield   |        |      |       |       |       |       |

| Name     | Offset     | Size  | Name       | Offset | Size | HWr   | HWw   | SWr   | SWw   |

| RO       | 0          | 16    | <i>B</i> 1 | 0      | 16   | False | True  | True  | True  |

| R1       | 1          | 16    | <i>B</i> 2 | 0      | 1    | True  | False | False | True  |

|          |            |       | <i>B</i> 3 | 1      | 1    | False | True  | True  | False |

|          |            |       | <i>B</i> 4 | 2      | 1    | False | True  | True  | False |

Table 32.1

Simple component register documentation table

```

entity SimpleRegs

2

port(

Generic Interface

3

Clk, Rst: in std_ulogic;

4

--- \acs{CPU} Interface

5

: in std_logic_vector(15 downto 0);

6

Addr

7

DataIn : in

std logic vector(15 downto 0);

En, Wr : in std logic;

8

DataOut : out std_logic_vector(15 downto 0);

9

10

- \acs{HW} Interface

11

R0 B1 i : in std logic vector(15 downto 0);

R0_B1_o : out std_logic_vector(15 downto 0);

12

13

R1 B2 o : out std_logic;

R1_B3_i : in std_logic;

14

R1 B4 i : in std logic

15

16

):

end entity regs;

17

18

architecture \acs{RTL} of SimpleRegs is

19

begin

20

SW_WRITE: process( Clk, Rst )

21

if Rst = '1' then

22

R1 B2 o <= '0'; R0 B1 o <= (others => '0');

23

elsif rising_edge ( Clk ) then

if En = '1' and Wr = '1' then

24

25

case Addr is

26

when B"0000 0000 0000 0000" => R0 B1 o <= DataIn;

27

when B'' 0000 0000 0000 0001'' \Rightarrow R1 B2 o \ll DataIn(1);

28

29

end case:

end if;

30

endif;

31

32

end process;

SW READ: process ( En, Addr )

33

begin

34

if En = '1' and Wr = '0' then

35

case Addr is

36

when B"0000_0000_0000_0000" =>

37

DataOut \leq R0_B1_i;

38

when B"0000_0000_0000_0001" =>

39

DataOut \stackrel{-}{<=} "0" \& R1_B3_i \& R1_B4_i \& B"0_0000_0000_0000";

40

when others => DataOut <= X"0000";

41

end case;

42

else

43

44

DataOut <= X'' 0000'';

45

end if;

end process;

46

end architecture RTL;

47

```

Fig. 32.3 VHDL file

storing the bitfield values written by the software. The second process is responsible for the multiplexers needed to provide the right value to SW via the port DataOut. The bitfields which cannot be accessed from SW are simply omitted. Similarly, only those bitfields marked to be SW readable contribute to the value to be passed to SW. All bits of a register with no bitfield contribution are filled with 0 as shown in line 40. If a bitfield is written and read from the same party – as the case for bitfield B1 of our example – then the IP-HW is responsible to feed either the same value back or a different one. It is worth noting that it is therefore not guaranteed that the same value which is written is read back.

For each bitfield that is read by the hardware, a port is created. Port  $R0_B1_0$  in line 12 illustrates the format of the names of these ports: They consist of the name of the register the bitfield is part of (R0), the bitfield's name (B1), and a character indicating the direction ( $\circ$ ). These elements are concatenated to the port name with underscores (\_).

Correspondingly, ports are created for bitfields written by the hardware. Finally, for each bitfield's port, a type is selected which both matches with its size and can be merged to a legal value of DataOut.

#### **C-Header File**

Figure 32.4 shows a possible firmware view of the HW/SW interface. For each register, a struct with elements representing the bitfields is created. The size of a bitfield is defined using the ":" operator followed by the size. The type is always uint16\_t indicating a 16-bit wide unsigned integer. The keyword volatile indicates that the bitfields may be modified outside the software. The compiler thus cannot cache the values, e.g., in a CPU register or optimize the number of read accesses and must access the raw bitfield every time it is used by the software (i.e., generally the C-code).

The registers are then combined to an overall register interface reg\_t using another struct. Assuming an instance SimpleInst0 and a pointer called SimpleInst0Ptr (see Line 17), then bitfield b2 can be accessed by:

SimpleInstOPtr->r1.b2

However, different C compilers won't accept this coding style since ":" is not generally supported. Further, unit16 t may not result in the intended result.

```

struct r0 t {

volatile uint16 t b1 : 16;

2

3

3:

4

5

struct r1 t {

volatile uint16 t b2

6

: 1;

volatile uint16 t b3 : 1;

7

volatile uint16_t b4 : 1;

8

9

const uint32_t unused : 13;

10 };

11

struct reg_t {

12

13

volatile r0 t r0;

14

volatile r1 t r1;

15 };

16

reg t *SimpleInst0Ptr;

```

Fig. 32.4 C-header file

```

struct reg_t {

volatile bus_t r0;

2

3

volatile bus t r1;

4

};

5

reg t *SimpleInstOPtr;

6

7

inline bool GetR1B3(reg t *rp) {

8

return (bool) ( (rp \rightarrow r1) >> 1 ) & 0x01 );

9

10

}

```

Fig. 32.5 Another C-header file

To address this, a style similar to Fig. 32.5 might be needed. Here, inline functions are used to access the bitfields. Line 8 shows how access to the bitfields is provided using a combination of shift, mask, and type cast.

There may be even more styles and variants of C's HW/SW interface view since bus\_t and bool may not be supported. For example, macros could be used instead of inline functions. For an overview of different coding styles, see, e.g., Chap. 5 "Hardware/Software Interface" of [6]. The important aspect of the metamodeling approach is the guaranteed consistency of all these views which is ensured by code generation from the same specification source.

So far, we have only seen a model as instance of a metamodel and as an *additional* view to all the existing views. Before identifying the case for metamodeling in Sect. 32.2.4, let's discuss the metamodeling terminology and take a look at the evolution of metamodeling over the last decades.

## 32.2.2 Terminology

#### 32.2.2.1 Metamodel

So far, we simply accepted the term *metamodel* as something that constrains a model but we did not dig deeper into the prefix *meta*. As opposed to metaphysics, which is not a specific domain of physics but a branch of philosophy, metamodeling is a term from computer science.

The relationship between both terms is that *meta* stands for *beyond*. While metaphysics deals with questions about *the fundamental nature of being* [13], metamodeling deals with *fundamental concept of a model*. Therefore, a *metamodel* models the domain of a model. In other words, a *metamodel* is a model of a model.

This definition is in line with the things that were already said about metamodeling. Our simple metamodel example models the domain of the HW/SW interface. It is a guide – and also a constraint – for each specific model of the HW/SW interface of a component.

#### 32.2.2.2 Metametamodel

There is however also a metamodeling domain. The models of this domain are *metamodels*. These models of the metamodeling domain in turn have their own

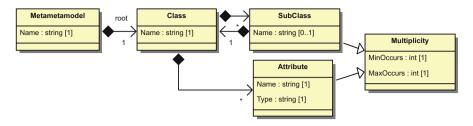

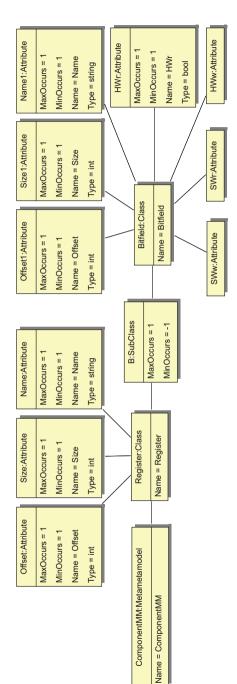

Fig. 32.6 Meta-metamodel

metamodels describing them. In other words, each model of the metamodeling domain (a *metamodel*) is an instance of its own metamodel; the metamodel thus has a metamodel. When viewed from the modeling domain, each model m has a metamodel mm. As this metamodel mm also has a metamodel, the latter is the meta-metamodel mmm of m.

An example of a meta-metamodel is shown in Fig. 32.6. It describes that a metamodel has a root class which has other classes and attributes, both of them in any multiplicity. Therefore, a class references a container for a subclass, which potentially redefines the name and specifies the multiplicity. For simplicity, base classes are not shown here. This does not reduce the expressiveness of the meta-metamodel since they do not contribute to the modeling possibilities as such.

Interestingly, this meta-metamodel can be defined using the formalism that is also used for the metamodel. This concept is not unusual in computer science. For example, the BNF grammar can be defined using an BNF grammar itself (see [34]). This is a hint that there might not be a *meta-meta-metamodel*, although there is some research to find this even more basic model.

Figure 32.7 shows the component metamodel from Fig. 32.1 as an instance of the meta-metamodel shown in Fig. 32.7. The object ComponentMM is the root node in the meta-metamodel instance named ComponentMM. Its only associated object Register of type Class is the root node of the metamodel. Its associated objects Offset, Size, and Name of type Attribute specify the attributes of Register. The object Register also has an associated Subclass object defining that the associated object Bitfield of type Class. The multiplicity 1...\* of this association is represented by MaxOccurs=1 and MinOccurs=-1. The Bitfield class has seven attribute objects associated with, three of which are not completely shown.

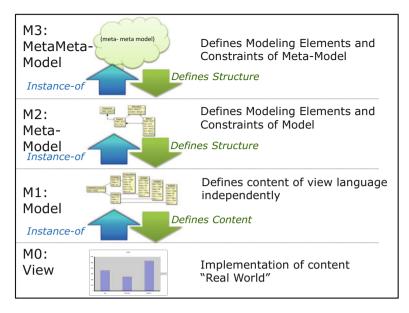

#### 32.2.2.3 Metamodeling Layers

The relationships of the introduced artifacts, views, models, metamodels, and metametamodels, are pictured in Fig. 32.8. Here, we see that the artifacts are labeled from M0 to M3, a terminology introduced by OMG (see [22]). We also see that the higher numbered artifacts define the structure of their directly lower numbered artifact. In turn, the lower labeled artifacts are an instance of – or in other words comply to – their directly higher numbered artifact. The M0-M1 relation differs as

Fig. 32.8 View, model, metamodel, and meta-metamodel

it is a content wise and not a structural dependency. In some cases, this dependency may also be structural, as the introduction of model-to-model transformations in Sect. 32.4.2.3 shows.

Although the depicted designation of layers is widely accepted, there are two alternative approaches. A small set of publications follow the idea that HW design deals with models, i.e., what we call a view is in their definition a model. Consequently, what we refer to as models, metamodel, and meta-metamodels becomes metamodel, meta-metamodel, and meta-meta-metamodel. This definition however is not that useful in the HW/SW interface domain, since neither documentation nor the C-code are models.

Another definition of layers is used in the Eclipse Modeling-Framework (EMF) world (see Sect. 32.4.1.4). Here, the running program embedded in the Eclipse framework is seen as *world*, i.e., being level M0. Unfortunately the data of the program is nothing else than our model. Since they are part of the "world," a *model* in the Eclipse terminology defines the structure of the data, which is – in our terminology – a *metamodel*. Consequently, the terminology is shifted one level down and only has view, model, and metamodel.

For the rest of the book chapter, we will follow the widely used OMG definition as depicted in Fig. 32.8.

## 32.2.3 History and Known Technologies

Metamodeling is not as new as it sounds. The basic idea was introduced about 40 years ago by Chen. In those days, it was called entity-relationship model (see

[3]). Most of the metamodeling concepts introduced above were either already there or introduced some years later by Smith and Smith (see [29]). From there on, they were continuously improved, especially in the domain of databases. It is therefore no surprise that there is still a relationship between database schemas and metamodels. Entity relationship diagrams were also used in the definition phase of the Jessi Common Framework Initiative (see e.g., [35]), now used to define entities in the hardware domain. First, mainly structurally oriented entities were modeled. The definition of the *EDIF Information Model* by Kahn (see [18]) used the entity-relationship methodology also named information model here. Due to complexity, it was expressed in a textual form using the EXPRESS notation (see [26]). The entity-relationship notation was however not limited to structural things. Soon later Kahn and Guimale defined an information model for VHDL that covered behavior and time as well [14]. A summary of all the work around entity-relationship models of hardware was collected in [2]. Here, the term *metamodeling* was already used in conjunction with hardware modeling.

Unfortunately, research activities around metamodeling in the hardware domain cooled down for a while. The Open Access Database (see [15]), intended to store hardware design data, was, for example, associated with an API, however not with an unambiguous metamodel. Fortunately, metamodeling grew further in the software world under the umbrella of the OMG. The design of XML, UML, and other technologies was based on metamodels.

## 32.2.4 The Case for Metamodeling

After having seen that metamodeling is not that new a concept in hardware design, this section now discusses the benefits of metamodeling in the design process. We ended Sect. 32.2.1.2 with the statement that so far, metamodeling is just an additional view in the design of the HW/SW interface. The following carves out the benefits of metamodeling, making it a very useful technology in the TLM area and HW/SW interface automation area.

The first benefit is that the views illustrated in this chapter's examples – and many more – can be generated from a model. Therefore, generators have to be built that translate the content of the model to the syntax of the target view. So, all but one view – the model – can be completely derived from the model and no longer need to be developed manually.

The second benefit is that the content of the model must not necessarily be entered manually. Often, parts of the model are already defined in a specification. By providing a specification reader – or a single source for specification and model – additional time can be saved and consistency between specification and design views can be improved, if not guaranteed.

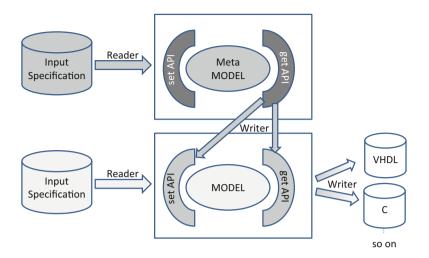

The third benefit is that big parts – especially the APIs – of the software needed to read the specification and to write the views can be automatically generated from a metamodel. Going hand in hand with that step, a good documentation via the metamodel diagram and a consistent way of treating models is achieved. This

Fig. 32.9 Concept of a metamodeling framework

is nothing else than the application of modeling and generation techniques to the construction of the automation tools.

All this is summarized in Fig. 32.9. Since not stated explicitly yet, a further detail worth noting, the APIs needed to handle different metamodels can be also generated from the meta-metamodel.

In order to build such a framework in a safe way, a good formal basis is needed. Diagrams, as shown so far, give a good overview but are less suited to define all details. In the next part of this chapter, we therefore introduce the formal definition of models and metamodels.

## 32.3 A Formal Model of Metamodeling

This section provides a formalization of metamodels, their models and the relation between metamodel and model. The representation used in the following is based on a set-oriented perspective on models. This approach was selected as it permits an intuitive description of the constraints metamodels impose on their models.

## 32.3.1 Basic Definitions

Models consist of correlated objects which contain attributes. Both the correlations and the attributes are named. Moreover, the attributes are multisets that contain some values. The following definitions provide a formal definition of these names and of the values that can be stored in model attributes.

## 32.3.1.1 Legal Names N of Correlations and Attributes

All legal names in a model are grouped in the set N. In this formal model, we define this set as a set of words over an alphabet  $\Sigma$ . The characters selected for this alphabet can be picked from an arbitrary set. It is convenient to rely on a set of words that can be easily mapped to potential view languages (i.e., words that are legal identifiers in common programming and modeling languages). Equation 32.1 defines such a set N of valid names:

$$\Sigma_{alphabet} = \{a, \dots, z, A, \dots, Z\}, \ \Sigma_{numeric} = \{0, \dots, 9\}$$

$$N = \mathscr{L}(\Sigma_{alphabet}(\Sigma_{alphabet}|\Sigma_{numeric})^*)$$

(32.1)

where  $\mathscr{L}(e)$  describes the set of the regular language defined by the regular expression *e*.

#### 32.3.1.2 Legal Values for Attributes

Attributes in models are typed. These types define the possible values an attribute can take and their interpretation. In this formal representation, type  $T_0$  is defined by a set. This set contains all the values this type allows. An attribute of type  $T_0$  can only take values  $v \in T_0$ .

In this formal model, some predefined types are provided. Each element in  $T = \{I, B, F, S\}$  defines such a type. Each type  $T_0 \in T$  is a set, containing all the values an attribute of the type  $T_0$  may take.

The predefined sets have the following content:

- S := Σ\* := {w<sub>0</sub>...w<sub>n</sub>|n ∈ ℕ} ∪ {ε} is the set defining the language of all valid strings. ε is the empty word and Σ is the alphabet of all possible characters.

- *I* is the set of all words representing valid integers.

- *F* is the set of all words representing valid floating point numbers.

- $B := \{True, False\}$  are the truth values of propositional logic.

The string type S occupies a special position here: It is a superset of any other type. Consequently, it contains any value an attribute – regardless of its type – may take:

$$\forall T_0 \in T : T_0 \subseteq S \tag{32.2}$$

Each of sets introduced above has an infinite number of elements. Metamodeling environments have predefined types such as integers of limited sizes and floating point numbers of various precision, originating from the runtimes used or the programming languages they are implemented in. They therefore provide subsets, constraining the range of integers, the precision of floating point numbers, and the length of elements in S which makes all type sets finite.

To work with attribute values, the metamodeling environment has to be able to interpret the elements in the type sets. For example, integers are used in the metamodel to define the minimum and maximum multiplicities of elements in the model. To enforce these definitions and to work with the information they provide, the metamodeling environment has to understand the integer type: It has to provide a bijective mapping INT:  $I \rightarrow \mathbb{Z} \cup \{\infty\}$ . Using this and other mappings, a runtime environment can define operators such as addition and multiplication on integer or floating point numbers.

## 32.3.2 A Formal Representation of a Model

## 32.3.2.1 The Set of All Models

This formal representation of models puts emphasis on the fact that everything is a model. Section 32.2.2 illustrates that what is a model exclusively depends on the point of view on the modeled system. Any model A becomes a metamodel not by definition but because it is instance of a model we perceive as meta-metamodel. Likewise, a model A can become a metamodel if there is a model C that is an instance of A.

The set of all models M therefore contains models, metamodels, and the metametamodel. Every model  $m \in M$  that is part of this set has the same structure which is defined in the following.

## 32.3.2.2 Definition of a Model

Each model  $m \in M$  is a tuple

$$m = (n, mm, O) \tag{32.3}$$

where  $n \in N$  is the name of the model (an element from the set of all identifiers).  $mm \in M$  is the metamodel which *m* is instance of. The main part of the model is the set of objects *O*. It contains the actual elements of a model.

## 32.3.2.3 The Set of All Objects O of a Model

Each object  $o \in O$  is a tuple:

$$o = (c, i, A, K, R)$$

(32.4)

where

• *c* is the class definition of the object. This definition is an object of the metamodel the model adheres to:

$$\forall m \in M, \ \forall o \in m.O : o.c \in m.mm.O \tag{32.5}$$

• *i* ∈ *I* is the name or unique identifier of the object. As the name suggests, there are never two objects in a model which have the same identifier:

$$\forall o_i, o_j \in m.O : o_i.i = o_j.i \Leftrightarrow o_i = o_j \tag{32.6}$$

• *A* is a set of object specific attributes where each attribute *a* ∈ *A* is a tuple of name and assigned values:

$$a = (n \in N, E), \quad E \subseteq S \tag{32.7}$$

n is the name of the attribute and E is a multiset containing the attribute's values. If an attribute contains several identical values, the multiset E contains the value several times. For each attribute, there is only one tuple in an object's o.A set. Equation 32.8 shows that if an attribute contains multiple values, these values are all in the multiset of the same attribute tuple.

$$\forall a_i, a_j \in o.A : a_i.n = a_j.n \Rightarrow a_i = a_j \tag{32.8}$$

The following will look at the elements *K* and *R* of the object tuple *o*. Analogous to the set of attributes *A*, both *K* and *R* are of a set of tuples  $(n \in N, E)$ , where *n* is a name and *E* is a set of values:

• K describes the children of the object o. Each element  $k \in K$  is a tuple

$$k = (n \in N, E), \quad E \subseteq I \tag{32.9}$$

• *R* is the set of referenced objects. *R* describes referenced elements, a concept we did not yet introduce. They are still included here as they are an essential part of all modern metamodeling frameworks. References allow elements inside models to refer to other elements at object granularity. They can be compared to attributes containing a pointer to other objects instead of an attribute value. Each element  $r_k \in R$  is a tuple

$$r = (n \in N, E), \quad E \subseteq I \tag{32.10}$$

Despite their largely similar structure, elements E which are part of tuples belonging to K and R have a different interpretation than elements belonging to tuples in A. The elements in E of an attribute contain actual values. In contrast, the elements E in a reference tuple r or child tuple k contain unique identifiers of other objects in the same model.

*Example 1.* The formal representation can now be used to describe any models as an element  $m \in M$ . Figure 32.10 provides an example for such a description. The model depicted here is the same model we used for our introductory example in Fig. 32.2.

**Further Constraints** Aside from the straightforward constraints already mentioned in the definition of the object tuple *o*, there are several further constraints:

• For every element  $e \in E$ , there is an object in the same model which has an identifier defined by the reference target t:

$$\forall m \in M, \ o_i \in m.O, \ r \in o_i.R, e \in r.E : \exists o_j \in m.O : o_j.i = e \qquad (32.11)$$

,

$$\begin{split} m.O &= & \left\{ o_{Simple}, o_{R0}, o_{R1}, o_{B1}, o_{B2}, o_{B3}, o_{B4} \right\} \\ o_{Simple} &= & \left( o_{Component}, 1, \left\{ (n_{Name}, \left\{ \texttt{Simple} \right\} ) \right\}, \\ & \left\{ (n_{Register}, \left\{ 2, 3 \right\} ) \right\}, \phi \right) \\ o_{R0} &= & \left( o_{Register}, 2, \left\{ (n_{Name}, \left\{ \texttt{RO} \right\} ), (n_{Offset}, \left\{ 0 \right\} ), (n_{Size}, \left\{ \texttt{16} \right\} ) \right\}, \\ & \left\{ (n_{Bit fields}, \left\{ \texttt{4} \right\} ) \right\}, \phi \right) \\ o_{R1} &= & \left( o_{Register}, 3, \left\{ (n_{Name}, \left\{ \texttt{RO} \right\} ), (n_{Offset}, \left\{ 0 \right\} ), (n_{Size}, \left\{ \texttt{16} \right\} ) \right\}, \\ & \left\{ (n_{Bit fields}, \left\{ 5, 6, 7 \right\} \right\} \right\}, \phi \right) \\ o_{B1} &= & \left( o_{Bit field}, 4, \left\{ (n_{Name}, \left\{ \texttt{B1} \right\} ), (n_{Offset}, \left\{ 0 \right\} ), \\ & \left( n_{SWr}, \left\{ \texttt{False} \right\} \right), (n_{HWw}, \left\{ \texttt{True} \right\} ), \\ & \left( n_{Size}, \left\{ \texttt{16} \right\} \right\}, \phi \phi \right) \\ o_{B2} &= & \left( o_{Bit field}, 5, \left\{ (n_{Name}, \left\{ \texttt{B2} \right\} ), (n_{Offset}, \left\{ 0 \right\} ), \\ & \left( n_{Size}, \left\{ \texttt{16} \right\} \right\} \right), \phi \phi \right) \\ o_{B3} &= & \left( o_{Bit field}, 6, \left\{ (n_{Name}, \left\{ \texttt{B3} \right\} ), (n_{Offset}, \left\{ \texttt{1} \right\} ), \\ & \left( n_{Size}, \left\{ \texttt{1} \right\} \right\} \right), \phi \phi \right) \\ o_{B4} &= & \left( o_{Bit field}, 7, \left\{ (n_{Name}, \left\{ \texttt{B4} \right\} ), (n_{Offset}, \left\{ \texttt{2} \right\} ), \\ & \left( n_{Size}, \left\{ \texttt{1} \right\} \right), \phi \phi \right) \\ o_{B4} &= & \left( o_{Bit field}, 7, \left\{ (n_{Name}, \left\{ \texttt{B4} \right\} ), (n_{HWw}, \left\{ \texttt{False} \right\} ), \\ & \left( n_{Size}, \left\{ \texttt{1} \right\} ), \phi \phi \right) \\ \end{array} \right) \\ \end{array}$$

Fig. 32.10 An example of a model in its formalized representation

Because of Eq. 32.6, there is exactly one element for every identifier and the reference is unique.

• Every object can be child of at most one element. In other words, every object has at most one parent. If we pick any two *different* objects  $o_i$  and  $o_j$  of the same model (therefore part of the same set m.O) and compare the intersection of their sets of children  $o_i$ . K and  $o_j$ . K, we will find that it is the empty set. Equation 32.12 illustrates that this is true if and only if we look at two different objects  $o_i$  and  $o_j$ .

$$\forall o_i, o_j \in m.O \ \forall k_i \in o_i.K, k_j \in o_j.K : k_i.E \cap k_j.E \neq \phi \Leftrightarrow o_i = o_j$$

(32.12)

Every object is child of exactly one other object except for one object which is said to be the model's root. Equation 32.13 shows that there is exactly one object for which no other object exists that contains the object in its set of children (∃! is the uniqueness quantification operator stating that *there is one and only one*)

$$\exists ! o_i \in m.O \ \exists o_j \in m.O, \ k \in o_j.K : o_i.i \in k.E$$

(32.13)

• The child relationship defines a hierarchy. For any two objects  $o_i, o_j \in O$  where  $o_i$  is direct or indirect child of  $o_j, o_j$  must not be direct or indirect child of  $o_i$ . For any sequence of objects where each object is child of its predecessing object, the first object and the last object must not be equal:

$$\forall (o_0, \dots, o_n) \in O^{n+1} \; \forall i \in [0, n-1] : \exists k \in o_i . K : o_{i+1} . i \in k . E$$

$$\Rightarrow o_0 \neq o_n \qquad (32.14)$$

• The constraint from Eq. 32.8 also applies to *o*.*K* and *o*.*R*.

In addition to that, the names n are not only unique within the attributes, children, and references of one object but also across the whole object. If an object has an attribute with the name  $n_0$ , there must not be any reference or child which has the same name. In other words, children, attributes, and references share the same namespace. The pairwise intersection of all child names, all attribute names, and all reference names must therefore be empty:

$$\forall o \in O \ \forall a, b \in o.K \cup o.A \cup o.R : a.n = b.n \Leftrightarrow a = b \tag{32.15}$$

Sets of All Models, Metamodels, and Meta-Metamodels This formal model defines three layers of models as illustrated in Fig. 32.8 of Sect. 32.2.2. These three layers are formalized here as three sets M, MM, and MMM. The largest of these sets is the set of all models M which was already introduced in the beginning of Sect. 32.3.2.

A metamodel  $mm \in MM$  is a model that describes the structure of a model. A model  $m_a \in M$  becomes a metamodel through the existence of a model  $m_b \in M$  which is an instance of it. Metamodels are therefore also models and the set of metamodels is given by

$$mm = \{m \in M \mid \exists m_b \in M : m_b.mm = m\}$$

(32.16)

A model becomes a meta-metamodel through the existence of a metamodel which is instance of it. The set of meta-metamodels is therefore given by

$$MMM = \{m \in M \mid \exists m_b \in MM : m_b.mm = m\}$$

(32.17)

It is obvious that  $MM \subset M$  and  $MMM \subset M$ . As any meta-metamodel necessarily has an instance, it is also a metamodel and the two equations simplify to  $MMM \subset MM \subset MM \subset M$ :

$$\forall mmm_i \in MMM \ \exists m \in MM : \ m.mm = mmm_i \Rightarrow mmm_i \in MM$$

(32.18)

Based on this definition and the assumption that there is only one meta-metamodel, it is trivial that the meta-metamodel is its own metamodel:

$$\exists mmm_j \in MMM \mid mmm_i.m = mmm_j$$

$$|MMM| = 1 \Rightarrow mmm_j = mmm_j$$

(32.19)

The meta-metamodel can therefore be used to describe itself. Equivalent notations for this are mmm. = mmm or mmm = (n, mmm, O)

$$\forall mm_1, mm_2 \in MM : mm_1.mm = mm_2.mm = mmm$$

(32.20)

## 32.3.3 Metamodel Constraints on Models

~

~

In a bottom-up approach, the formal definition of models in formal models presented section 32.3.2.2 already lists some constraints on models that originate from the meta-metamodel we agreed on.

In the following, we complement this with other constraints a metamodel mm imposes on its models *m*. Approaching the problem top-down, we first declare names for attributes and objects of the meta-metamodel:  $n_{name}$ ,  $n_{ref}$ ,  $n_{comp}$ ,  $n_{attr}$ ,  $n_{min}, n_{max}, n_{type} \in N$ . Next, a formal description of the meta-metamodel mmm as instance of itself is developed. Finally, a list of constraints is provided.

**Meta-Metamodel** Any metamodel can then be uniquely represented as instance of this meta-metamodel *mmm*: ~

$$o_{class}, o_{composition}, o_{reference}, o_{attribute} \in mmm.O$$

$$o_{class} = (o_{class}, 1, A_{name}, K_{class}, \phi)$$

$$o_{composition} = (o_{class}, 2, A_{name} \cup A_{multiplicity}, \phi, R_{class})$$

$$o_{reference} = (o_{class}, 3, A_{name} \cup A_{multiplicity}, \phi, R_{class})$$

$$o_{attribute} = (o_{class}, 4, A_{name} \cup A_{multiplicity} \cup A_{types}, \phi, \phi)$$

$$A_{name} = \{(n_{name}, N)\}$$

$$A_{multiplicity} = \{(n_{max}, I \cup \{\infty\}), (n_{min}, I)\}$$

(32.21)

Set of legal integer values

$$I \subset S$$

C 100 100 100 0

$$A_{types} = \{(n_{type}, \underbrace{S}_{\text{Support of an approximation of } S})\}$$

Set of all possible strings. Superset of any possible type-set  $T_i$ .

$$K_{class} = \{(n_{comp}, \{2\}), (n_{ref}, \{3\}), (n_{attr}, \{4\})\}$$

$$R_{class} = \{(n_{type}, \{1\})\}$$

~

Metamodels instantiate these uniquely named objects and provide values for their attributes. What we described above is in fact both the description of the metametamodel mmm and a metamodel mm (as it is instance of mmm).

We can now use the description of the meta-metamodel and provide formulae for how metamodel objects constrain their models. These descriptions are simplified by a set of helper functions.

**Helper Functions** The functions  $O_{A,mm}$ ,  $O_{K,mm}$ , and  $O_{R,mm}$  are defined for any model *m*. They map any object of the model to the set of metamodel objects that describe its attributes  $(O_{A,mm})$ , children  $(O_{K,mm})$ , and references  $(O_{R,mm})$  or a combination thereof  $(O_{KR,mm}, O_{KRA,mm})$ . In programming, such a mapping is called introspection. Each of them therefore maps from the pre-image set m.O of any model to the image set  $\mathcal{P}(m.mm.O)$ :

$$O_i: m.O \to \mathscr{P}(m.mm.O) \tag{32.22}$$

The function  $\mathscr{P}(X) := \{U \mid U \subseteq X\}$  maps any set X to its powerset.

$$O_{A,mm}: o \mapsto \{o_i \in mm.O \mid \exists k \in o.c.K : o_i.i \in k.E \land k.n = n_{attr}\}$$

$$O_{K,mm}: o \mapsto \{o_i \in mm.O \mid \exists k \in o.c.K : o_i.i \in k.E \land k.n = n_{comp}\}$$

$$O_{R,mm}: o \mapsto \{o_i \in mm.O \mid \exists k \in o.c.K : o_i.i \in k.E \land k.n = n_{ref}\}$$

$$O_{KRA,mm}: o \mapsto O_{A,mm}(o) \cup O_{K,mm}(o) \cup O_{R,mm}(o)$$

$$O_{KR,mm}: o \mapsto O_{K,mm}(o) \cup O_{R,mm}(o)$$

(32.23)

Moreover, the function  $E_{name}$  returns the set of all values of an attribute provided the attribute name. The function  $o_{bvid}$  returns an object given by its unique identifiers:

$$E_{name}: O \times N \to \mathscr{P}(S), \quad (o, n) \mapsto \{e \in S \quad | \quad \exists y \in o.A \cup o.R \cup o.K, \\ y.n = n : e \in y.E\}$$

$$o_{byid}: M \times I \to O \qquad (m, i) \mapsto o \in m.O \quad | \quad o.i = i$$

(32.24)

**Constraints** The following constraints are valid for any model m of metamodel mm:

• For each attribute, composition, and reference, the metamodel restricts the minimum and maximum number of elements that are contained or referenced. This number is commonly referred to as multiplicity:

(32.25)

$$\forall y \in o.A \cup o.K \cup o.R, \ o_{mm} \in O_{KRA,mm}(o), \ e_{max} \in E_{name}(o_{mm}, n_{max}) :$$

$$y.n \in E_{name}(o_{mm}, n_{name}) \Rightarrow \operatorname{INT}(e_{max}) \geq |y.E|$$

$$Y \in \{K, R, A\} \ \forall o_{mm} \in O_{Y,mm}(o), \ e_{min} \in E_{name}(o_{mm}, n_{min}) \ \exists y \in o.Y :$$

$$y.n \in E_{name}(o_{mm}, n_{name}) \land \operatorname{INT}(e_{min}) \leq |y.E|$$

• For each attribute, the metamodel constrains the values that it can take. To do this, the metamodel object defining the attribute has a type property listing all possible values:

$$\forall a \in o.A, \ o_{mm} \in O_{A,mm}(o): \qquad a.n \in E_{name}(o_{mm}, n_{name}) \\ \Rightarrow a.E \subseteq E_{name}(o_{mm}, n_{type})$$

(32.26)

• Compositions and target references are statically typed through the metamodel. For each composition element and each reference, the metamodel constrains the metamodel object the that the target is instance of:

$$\forall m \in M, \ y \in m.o.K \cup m.o.R, \ i_{target} \in y.E, \ o_{mm} \in O_{KR,mm}(o):$$

$$y.n \in E_{name}(o_{mm}, n_{name}) \Rightarrow o_{byid}(m, i_{target}).c.i \in E_{name}(o_{mm}, n_{type})$$

(32.27)

## 32.4 Metamodeling for HW/SW Codesign

## 32.4.1 Metamodeling Frameworks

The formal models presented in Sect. 32.3 lay the foundation for the correct design and construction of metamodeling frameworks. A first framework has already been sketched in Sect. 32.2.4. This section first discusses Model-Driven Architecture (MDA) and its impact on metamodeling frameworks. It then describes the metamodeling frameworks most widely used for automated design creation: XML, UML, and EMF. Next, standardized metamodels covering the HW/SW interface are introduced and the use of custom metamodels is motivated. Practical experience gained from the use of metamodeling in industrial applications finishes this section.

## 32.4.1.1 MDA

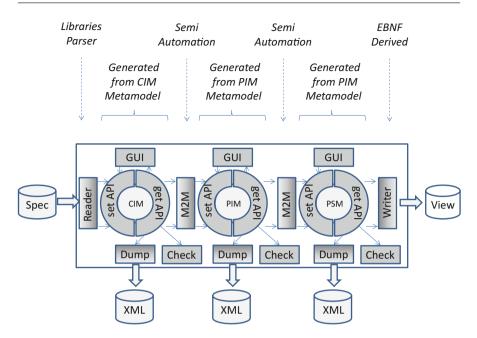

MDA – acronym for <u>Model-Driven Architecture</u> – is a vision of the Object Management Group (OMG) (see [23] and [32]) for automation of code development via metamodeling, model-to-model transformations, and code generation. In the simple approaches toward metamodeling sketched in Fig. 32.9, a specification is first read into a model via a reader and then translated to the view via a generator. To

Fig. 32.11 An advanced metamodeling framework

implement the full MDA vision, this simple approach is extended: The target view is not generated directly from the first model, which is still close to the specification. Instead, the view is generated from a model that is closer to the target view's structure and semantics. Since these two models may still differ too much, one or even more intermediate models might be introduced to further partition the translation. Figure 32.11 shows such a process with one additional intermediate model.

To structure this approach and to find criteria for the definition of the models involved, MDA introduces three levels of models:

PSM: A <u>Platform Specific Model</u> is very close to the target view. Model and view therefore have similar structure but different syntax. In addition, the Platform Specific Model has sufficient information about the environment of the final view. A good example for a PSM is the Abstract Syntax Tree (AST) of the view's underlying language which already includes references to libraries that are used in the programming or modeling environment of the platform. For the example of the hardware register view, the PSM would be the AST of VHDL with links to VHDL's synthesis packages and libraries of reusable components.

If view generation starts from a PSM, the view can also be seen as an instance of the model and not just the content of the model since the view follows the structure of the model.

PIM: A <u>Platform Independent Model</u> does not include platform details but already depends on the targeted implementation's semantics – or in SW terminology: It depends on the kind of computation being targeted.

A good example is a view's language independent structural model being able to handle components, their instantiations and connections between them. However, such a model does not consider language specifics as VHDL's component-based instantiation, its port signals types (e.g., std\_logic) and out semantics, or Verilog's wire-based style.

CIM: A Computation Independent Model focuses on items in the modeled domain, independent of their implementation. A very good example is the register model of our simple component, since it is independent of the target semantics (i.e., of a sequential programming language describing the SW access, of a TLM register model interfaced by a method, or of an event-driven VHDL model describing the HW part). This independence is precisely what is important for metamodels describing interfaces between domains. It is also easier to parse specification data into that model since a specification focuses on *what the design should do* and not on *how the design shall be implemented*.

In MDA, for each of the CIMs, PIMs, and PSMs, a metamodel is defined. This metamodel acts as the starting point and interface agreement for automation.

A metamodeling framework following the ideas of MDA is shown in Fig. 32.11. Here, the models are encapsulated in APIs with separate interfaces for writing and reading data (setAPI and getAPI). Using these interfaces, the data can be dumped into an intermediate storage based on the XML format, edited with a GUI or validated by check functions. These checks are derived from constraints provided by the metamodel or the meta-metamodel in use. All these components of metamodeling framework can be automatically generated using the metamodel description. Additional checks can be generated from OCL constraints associated with the metamodel or parts of it.

There are even several methods to automate the construction of translators. The view generator, for example, can either be derived from a metasyntax notation like EBNF or can be based on a template engine. The reader can, for example, make use of libraries or parser generators. All together, a metamodeling framework is a powerful tool that not only automates generation of views but also the construction of parts of the automation solution.

The metamodeling approach described in [8] and entitled *meta-synthesis* goes one step further. It also automates the building of automation tools by supporting merge and split of data during model-to-model transformation, dump and reload utilities for models, checks of model consistency, and execution control. Providing such a high level of automation makes it comprehensible how the use of models which are instances of metamodels helps to dramatically improve design productivity and design quality although the metamodels have to be built upfront.

In the following, we introduce the three metamodeling frameworks. EMF, synonym for Eclipse Modeling Framework, as well as XML and UML which describe both modeling languages and a modeling framework.

```

<?xml version="1.0" encoding="UTF-8"?>

1

<Component Name="Simple">

2

<Register Name="R0" Size="16" Offset="0">

3

<Bitfield Name="B1" Size="16" Offset="0"

4

HWr="false" HWw="true" SWr="true" SWw="true" />

5

</Register>

6

<Register Name="R1" Size="16" Offset="1">

<Bitfield Name="B2" Size="1" Offset="0"

7

8

HWr="true" HWw="false" SWr="false" SWw="true" />

9

<Bitfield Name="B3" Size="1" Offset="1"

10

HWr="false" HWw="true" SWr="true" SWw="false" />

11

<Bitfield Name="B4" Size="1" Offset="2"

12

HWr="false" HWw="true" SWr="true" SWw="false" />

13

</ Register>

14

15 </ Component>

```

Fig. 32.12 The simple component model in XML format

#### 32.4.1.2 XML

XML, acronym for eXtensible Markup Language, is a markup language that is used to store and annotate data. There are many books on XML and lots of web pages detailing the usage of the language in different fields of application. Instead of providing an overview over this vast area, this book focuses on the special features of XML that can be used in the context of metamodeling.

One of XML's initial goals was to separate content and view, an idea that also underlies the metamodeling concept. The mix of formatting and data – as, e.g., used in older versions of HTML – should be overcome to ease information retrieval and to support different publishing styles. The resulting XML standards were therefore shaped in a way that allowed storing data which could also be used to capture models of metamodeling environments. Figure 32.12 provides an example of our simple component model encoded in XML.

Of course, a representation similar to Fig. 32.12 can also be used to store metamodels. UML, for example, defines the <u>XML Metadata Interchange</u> (XMI) format as an XML-compatible markup language for storing models and metamodels. This XML Metadata Interchange (XMI) format is also used in the Eclipse EMF domain.

In addition, XML has a mechanism called  $\underline{X}ML$  Schema Definition (XSD) to define the valid structure of an XML document, effectively defining a metamodel for XML documents. XSD has a set of powerful features for specification of valid values. Similar to the formal definition in 32.3, XML and XSD only deal with strings. All values in the pictured XML file are therefore embedded in double quotes. An XSD schema specifies the valid strings an attribute may be assigned with and how those then have to be interpreted, e.g., as a number or a Boolean value. Figure 32.13 shows the XML schema defining the validity of the XML file in Fig. 32.12. It carries the same information as the metamodel that was introduced in the introductory example in Fig. 32.1. It is, however, not as intuitive as the graphical view of the metamodel. In addition, the requirements on well-formed XML documents make the format a bit verbose. XSD documents are formatted

```

<?xml version="1.0" encoding="UTF-8"?>

1

2 <xsd:schema xmlns:xsd="http://www.w3.org/2001/XMLSchema">

<xsd:element name="component" type="Component" />

3

4

<xsd:complexType name="Component">

<xsd:sequence>

5

6

<xsd:element name="register" type="Register" />

7

</ xsd:sequence>

<xsd:attribute name="Name" type="xsd:string" use="required" />

8

9

</ xsd:complexType>

<xsd:complexType name="Register">

10

11

<xsd:sequence>

<xsd:element name="bitfield" type="Bitfield" />

12

</ xsd:sequence>

13

<xsd:attribute name="Name" type="xsd:string" use="required" />

<xsd:attribute name="Offset" type="xsd:int" use="required" />

14

15

<xsd:attribute name="Size" type="xsd:int" use="required" />

16

17

</ xsd:complexType>

<xsd:complexType name="Bitfield" minOccurs="1" maxOccurs="unbounded">

<xsd:complexType name="Bitfield" minOccurs="1" maxOccurs="unbounded">

<xsd:attribute name="Name" type="xsd:string" use="required" />

<xsd:attribute name="Offset" type="xsd:int" use="required" />

18

19

20

<xsd:attribute name="Size" type="xsd:int" use="required" />

<xsd:attribute name="HWr" type="xsd:bool" use="required" />

21

/>

22

<xsd:attribute name="HWw" type="xsd:bool" use="required" />

23

<xsd:attribute name="SWr" type="xsd:bool" use="required" />

24

<xsd:attribute name="SWw" type="xsd:bool" use="required" />

25

26

</ xsd:complexType>

27 </ xsd:schema>

```

Fig. 32.13 Component metamodel in XSD format

in valid XML themselves. This allows existing XML parsers to read the schemas; however, it is also responsible for XSD's verbosity.

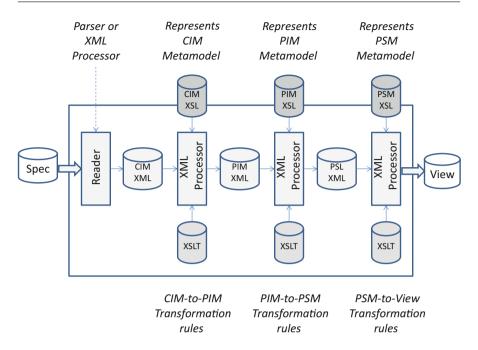

Specific to the XML-based MDA process is that the model is stored in a file and not in an encapsulated data model that is part of a program. This is shown in Fig. 32.14 on the same MDA flow as pictured in Fig. 32.11. Here, the transformations are done by XML processors which read XSLT, a transformation language for XML.

XSLT can also be used to translate XML to any kind of textual view such as C-code or VHDL models. The only thing needed to build an XML CIM in the depicted XML MDA flow is therefore a reader. If the specification is available as an XML document, this reader might be an XSLT-based translation as well.

#### 32.4.1.3 UML

UML is a widely used standard in the software world incorporating many concepts and notations that have proven to be successful. UML also defines an aligned graphical view on all the concepts included. The widespread adoption of UML brought a significant benefit compared to the situation before where different methodologies used different graphical notations for the same concepts or even the same notation for different concepts. UML as a whole however has a disadvantage: It is quite complex and some definitions are ambiguous.

All the notations – also called diagrams – are defined via a metamodel which in turn is defined on basis of a meta-metamodel. This UML meta-metamodel is called MOF (see [22]) – acronym for <u>Meta Object Facility</u>. Inside the MOF and essential MOF called EMOF and a complete MOF called CMOF is defined. Based on MOF, UML defines a standard intermediate called XMI which we already mentioned.

Fig. 32.14 MDA using XML

UML influenced metamodeling in many ways. Since UML diagrams also support behavioral notations like state or activity diagrams, it proves that metamodels are not restricted to structural information. Instead, a structure can be defined which has inherent execution semantics.

UML also supports class diagrams, which – or more precisely an extended subset of which – can be used to define metamodels in a graphical way. UML's EMOF is thus conceptually very close to a class diagram. This is obvious since a class diagram structures data and a metamodel structures its domain in entities (*classes*), their properties (*their attributes*), and their relation to other entities (*different kinds* of associations).

Last but not least, UML has a built-in extension mechanism, which permits the adaption of UML to different needs and domains. The adaptability to different needs in particular is a noteworthy benefit of a modeling-based approach over the tool-based approach in system-level automation.

*Stereotypes* can be used to create new model elements, represented by «...»brackets. These model elements may also have their own graphical representation. In addition, stereotypes can be used to create completely new diagrams including their graphical representation.

The second mechanism is *tagged values*. They used to define additional properties for existing modeling elements or stereotypes. They include additional information needed for specific use cases. This information can also influence further processing of the model. When our simple component metamodel is used for HW generation, it can be extended with tagged values describing how many flip-flop instances should be generated for every bitfield:

- Zero: Only wires would be generated in both directions.

- One: Only one flip-flop group written by SW (as depicted in Fig. 32.3)

- · One shared: Flip-flops writable by HW and SW

- Two: One flip-flop group being written by SW and read by HW as well as one flip-flop group being written by HW and read by SW

Other tagged values might specify if SW read and write accesses trigger pulses and edges at additional signals passed to the HW core.

It is important to note that tagged values modify the metamodel in an upward compatible way since they only add items. In contrast, UML's third adoption mechanism called *constraints* adds new rules or modifies existing ones. Constraints can be used to remove an attribute from a modeling element. Code generators that rely on a removed field would fail.

A set of any of the defined extensions can be packed and provided as a so-called profile. SysML (see Sect. 32.4.2.2) is one example of such a profile. These profiles are called lightweight extensions since they don't change UML's metamodel. In contrast, a heavyweight extension would add new items, concepts, and relationships to UML's MOF.

#### 32.4.1.4 Eclipse Modeling Framework

EMF, synonym for Eclipse Modeling Framework, is a full-featured metamodeling framework. EMF uses Java as implementation and glue language and generates a Java API as well as other things for the specified metamodel (e.g., an editor model). EMF is fully integrated in the Eclipse framework. EMF is a good starting point for metamodeling since it is open source and can easily be obtained from the Eclipse Foundation. EMF's web page (see [9]) refers to many online tutorials, webcasts, and video-casts. For those preferring old-style printed books, the key contributors to EMF collected an overview on EMF in [30]. There are also many forums around EMF helping with questions.

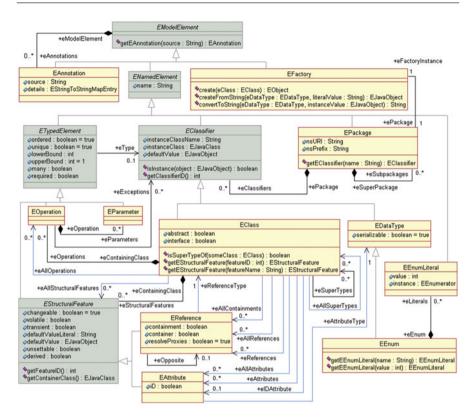

Diving into EMF is however not straightforward and it takes a while to get started with the framework. Many consulting companies around EMF offer their help. If someone prefers closed-source tools that come bundled with professional service, then he/she might look at the tools from MetaCase [20]. An important contribution of EMF to the metamodeling world is its meta-metamodel called ECORE. ECORE was designed to be able to map XML schema, UML metamodels (diagram types in UML terminology), and database schemas to one model. The ECORE model shown in Fig. 32.15 is conceptually identical to our first meta-metamodel shown in Fig. 32.6.

Figure 32.15 shows four additional modeling features: First, as already included in our formal model, ECORE has a reference mechanism implemented via EReference. This mechanism has similarities with association in EMOF. Via containment, references and compositions (the only hierarchical element in our

Fig. 32.15 EMF ECORE meta-metamodel [10]

simple metamodel) can be distinguished. Second, ECORE supports inheritance via eSuperTypes and eAllSuperTypes. Third, ECORE supports namespaces via EPackage. Fourth and last, ECORE supports enumerations via the EEnum and EEnumLiteral meta-classes.

Further, ECORE makes more use of inheritance. For example, all the naming is defined in the virtual classes EClassifier, ENamedElement, and EModelElement. Similarly, bounds and other features are derived from EStructrualFeature and ETypedElement.

The meta-class EFactory does not describe a modeling feature but methods to create the instances and to do string conversion. Finally, EAnnotation provides a measure to add data to the model that can be used, e.g., for view generation or model transformation.

Less obvious, yet just as important is that the API does not only permit access to the model. Instead, it also permits access to the metamodel items which are associated with the model items. In this way, introspection is supported for all model elements and meta-programming techniques can be applied. This allows different attributes to be handled by the same piece of code although they are differently typed. This facilitates the implementation of translators and view generators that support on any instance of one kind of meta-metamodel.

## 32.4.2 Related Standards

Around the XML metamodeling technology, two standards have been defined that are widely used in the HW/SW area: IP-XACT and SysML. This section gives an overview over the standards and afterward motivates the benefit of an application specific metamodeling approach.

## 32.4.2.1 IP-XACT

IP-XACT (see [19]) is a standard supporting automation of IP Integration and thereby automation of System-on-Chip (SoC) construction. A PDF version of the standard is available from the IEEE [16]. IP-XACT has wide professional support. Several Electronic Design Automation (EDA) tools support IP-XACT and almost all IPs have an associated IP-XACT view. There are also open-source tools supporting IP-XACT, e.g., Kactus2 (see [31]).

IP-XACT defines an XML Schema with additional semantic documentation of the schema items. From the modeling standpoint, IP-XACT primarily supports the definition of the following items:

- Signals, interfaces, and bus structures as elements for the connection of components.

- RTL, TLM, or mixed RTL and TLM connections.

- Components describing hardware blocks of the IP. To interface with the HW world components offer interfaces for complex signal bundles and simple ports. Further, they can have parameters. Finally, components include the definition of the register layout and thus define most parts of the IP's SW interface.

- Definition of connection of IPs in a so-called System Model.

From HW/SW perspective, only a subset of the features IP-XACT provides are of interest.

The System Model, since it defines the involved components, the number how often they are instantiated and the instance names. The definition of the base address for each instance and derived from that the based addresses of the register fields is an important key for efficient software development.

The way how registers are specified is more advanced than in our simple model. Components have addressable units specifying their own base address inside the address space of the component and their own address range. Furthermore, the addressable units can be connected to interfaces. Like this, registers can be addressed via two or more CPU buses or over other protocols such as Serial Peripheral Interface (SPI). Figure 32.16 illustrates that the registers in IP-XACT and our register model share a similar underlying concept: Components have registers and registers have bitfields.

```

1

<ipxact:register>

2

<ipxact:name>R0</ spirit:name>

3

<ipxact:addressOffset> 0x00 </ipxact:addressOffset>

4

<ipxact:size>16</ipxact:size>

5

<ipxact:field>

<ipxact:name>B1</ipxact:name>

6

7

<ipxact:bitOffset>0</ipxact:bitOffset>

<ipxact:bitWidth>16</ipxact:bitWidth>

8

9

<ipxact:access>read-write</ipxact:access>

10

<ipxact:volatile>true</ipxact:volatile>

</ipxact:field>

11

</ipxact:register>

12

13

<ipxact:register>

<ipxact:name>R1</ spirit:name>

14

<ipxact:addressOffset> 0x01 </ipxact:addressOffset>

15

<ipxact:size>16</ipxact:size>

16

<ipxact:field>

17

18

<ipxact:name>B2</ipxact:name>

<ipxact:bitOffset>0</ipxact:bitOffset>

19

20

<ipxact:bitWidth>1</ipxact:bitWidth>

<ipxact:access>write-only</ipxact:access>

21

22

<ipxact:volatile>false</ipxact:volatile>

</ipxact:field>

23

24

<ipxact:field>

25

<ipxact:name>B3</ipxact:name>

<ipxact:bitOffset>1</ipxact:bitOffset>

26

27

<ipxact:bitWidth>1</ipxact:bitWidth>

<ipxact:access>read-only</ipxact:access>

28