# Adaptive Streaming Applications: Analysis and Implementation Models

Jiali Teddy Zhai

## Adaptive Streaming Applications: Analysis and Implementation Models

#### **PROEFSCHRIFT**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op woensdag 13 mei 2015 klokke 10:00 uur

door

Jiali Teddy Zhai geboren in 1982

#### Samenstelling promotiecommissie:

Promotor: Prof. Dr. Ir. Ed F.A. Deprettere Universiteit Leiden Co-Promotor: Dr. Todor P. Stefanov Universiteit Leiden

Overige leden: Prof. Dr.-Ing. Jügen Teich Universität Erlangen-Nürnberg

Dr. Ingo Sander KTH Kungliga Tekniska högskolan Prof. Dr. Ir. Twan A.A. Basten Technische Universiteit Eindhoven

Prof. Dr. Joost N. Kok

Prof. Dr. Farhad Arbab

Universiteit Leiden

Universiteit Leiden

Universiteit Leiden

Universiteit Leiden

Adaptive Streaming Applications: Analysis and Implementation Models Jiali Teddy Zhai. -

Dissertation Universiteit Leiden. - With ref. - With summary in Dutch.

Copyright © 2015 by Jiali Teddy Zhai. All rights reserved.

This dissertation was typeset using LATEX in Linux. Cover designed by Shanshan Yang

Printed in the Netherlands.

## **Contents**

| Ta | ble o | f Contents                                           |          | V    |

|----|-------|------------------------------------------------------|----------|------|

| Li | st of | Figures                                              |          | ix   |

| Li | st of | Tables                                               |          | xiii |

| 1  | Intr  | roduction                                            |          | 1    |

|    | 1.1   | Embedded Streaming System Design                     |          | 2    |

|    |       | 1.1.1 Design Requirements                            |          |      |

|    |       | 1.1.2 Application Characterization                   |          |      |

|    |       | 1.1.3 Platform Implications                          |          | 7    |

|    |       | 1.1.4 Model-based Design Methodology                 |          |      |

|    |       | 1.1.5 Summary                                        |          | 14   |

|    | 1.2   | Problem Statement                                    |          | 15   |

|    | 1.3   | Research Contributions                               |          | 17   |

|    | 1.4   | Thesis Organization                                  |          | 19   |

| 2  | Mod   | dels-of-Computation (MoC)                            |          | 21   |

|    | 2.1   | Polyhedral Process Networks (PPN)                    |          | 21   |

|    | 2.2   | Actor-based Data Flow MoCs                           |          | 29   |

|    |       | 2.2.1 Synchronous Data Flow (SDF)                    |          | 30   |

|    |       | 2.2.2 Cyclo-Static Data Flow (CSDF)                  |          | 32   |

|    | 2.3   | Hard Real Time Scheduling of Acyclic (C)SDF Graphs   |          | 33   |

| 3  | Aut   | omated Analysis Model Construction: Deriving CSDF fi | om Equiv | -    |

|    | alen  | t PPN                                                | _        | 39   |

|    | 3.1   | The Algorithm                                        |          | 40   |

|    | 3.2   | Experimental Results                                 |          | 47   |

vi Contents

| 4  | •     | loiting Maximum Data-level Parallelism without Inter-processor |     |

|----|-------|----------------------------------------------------------------|-----|

|    | Con   | nmunication                                                    | 51  |

|    | 4.1   | Motivating Example                                             |     |

|    | 4.2   | Related Work                                                   | 57  |

|    | 4.3   | Finding all Dependences in a PPN                               | 58  |

|    | 4.4   | Computing the Number of Communication-free Partitions          | 60  |

|    | 4.5   | Communication-free Partitioning Algorithm                      |     |

|    | 4.6   | Experimental Results                                           |     |

| 5  | Exp   | loiting Just-enough Parallelism in Hard Real-time Systems      | 75  |

|    | 5.1   | Related Work                                                   | 77  |

|    | 5.2   | Unfolding of SDF Graphs                                        | 78  |

|    | 5.3   | Problem Formulation                                            | 80  |

|    | 5.4   | Period Scaling under Hard Real-time Scheduling                 | 83  |

|    | 5.5   | Bounding Solution Space                                        |     |

|    | 5.6   | The Algorithm                                                  |     |

|    | 5.7   | Experimental Evaluation                                        |     |

| 6  | A N   | lew MoC for Modeling Adaptive Streaming Applications           | 99  |

|    | 6.1   | Related Work                                                   | 100 |

|    | 6.2   | Model Definition                                               | 101 |

|    |       | 6.2.1 Parameterized Polyhedral Process Networks                |     |

|    |       | 6.2.2 Operational Semantics                                    |     |

|    | 6.3   | Consistency                                                    |     |

|    | 6.4   | Experimental Results                                           |     |

| 7  | Har   | d Real-time Scheduling of Adaptive Streaming Applications      | 115 |

|    | 7.1   | Related Work                                                   | 117 |

|    | 7.2   | Model Definition                                               | 118 |

|    |       | 7.2.1 Mode-Aware Data Flow (MADF)                              | 118 |

|    |       | 7.2.2 Operational Semantics                                    |     |

|    |       | 7.2.3 Mode Transition                                          |     |

|    | 7.3   | Hard real-time Scheduling of MADF                              | 130 |

|    |       | Case Study                                                     |     |

| 8  | Sum   | nmary and Outlook                                              | 145 |

| Bi | bliog | raphy                                                          | 149 |

| Sa | menv  | ratting                                                        | 163 |

| Contents | vi |

|----------|----|

|          |    |

| List of Publications  | 169 |

|-----------------------|-----|

| Index                 | 171 |

| List of Abbreviations | 173 |

## **List of Figures**

| 1.1 | Three examples of embedded streaming applications                                                                                                                                                                                    | 2               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

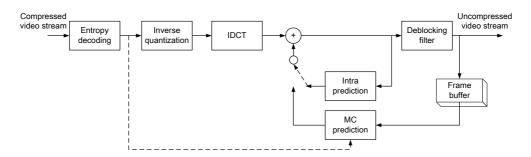

| 1.2 | Block diagram of a H.264 decoder (taken from [18]). Each task is represented by a rectangular block                                                                                                                                  | 5               |

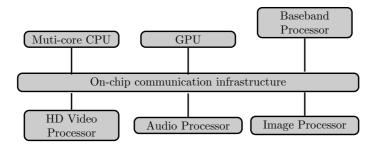

| 1.3 | Processing part of an MPSoC platform for mobile devices from Nvidia (taken and simplified from [11])                                                                                                                                 | 8               |

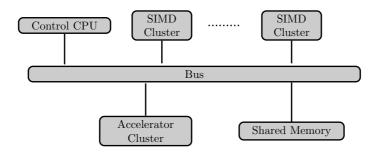

| 1.4 | Template of a baseband processor (taken and simplified from [103]). All interfaces and peripheries are omitted                                                                                                                       | 8               |

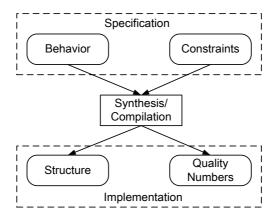

| 1.5 | X-chart: a general design process (adopted from [50])                                                                                                                                                                                | 9               |

| 1.6 | Comparison of dataflow MoCs for streaming applications (taken and extended from [112]). The MoCs underlined are proposed in this thesis.                                                                                             | 10              |

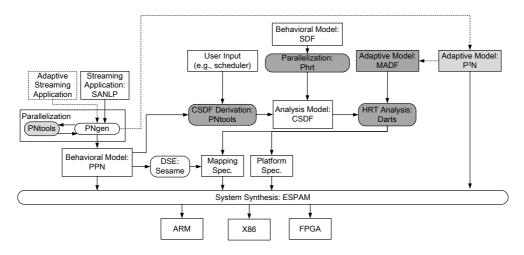

| 1.7 | Daedalus <sup>RT</sup> design flow. The grey boxes highlight the contributions of this thesis. The dashed box and lines denote the parts that are currently not fully implemented                                                    | 13              |

| 2.1 | A polyhedron                                                                                                                                                                                                                         | 23              |

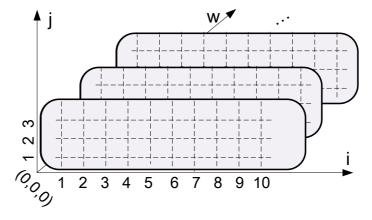

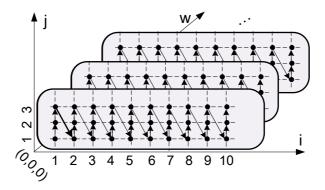

| 2.2 | The polyhedral representation of the execution of function read_imag in Listing 1                                                                                                                                                    | e<br><b>2</b> 9 |

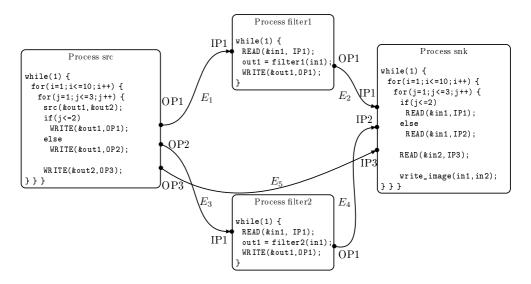

| 2.3 | PPN corresponding to the SANLP in Listing 1                                                                                                                                                                                          | 29              |

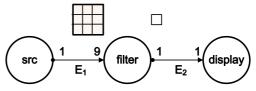

| 2.4 | An example of an image filter algorithm modeled using the SDF MoC.                                                                                                                                                                   | 30              |

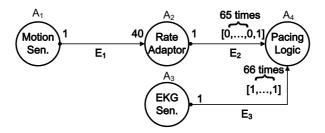

| 2.5 | A CSDF graph $G_1$ of a pacemaker application (taken from [99])                                                                                                                                                                      | 33              |

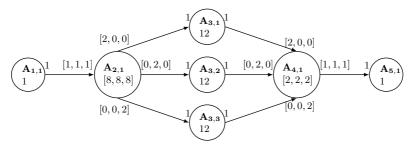

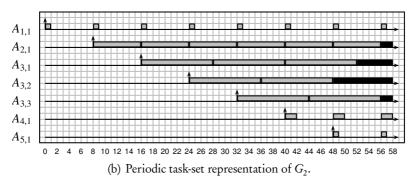

| 2.6 | An example of a CSDF graph and its real-time task-set representation. Since the execution of the actors repeats indefinitely, the last execution of $A_{2,1}$ , $A_{3,1}$ , $A_{3,2}$ , and $A_{3,3}$ in the figure is truncated and |                 |

|     | shown in black                                                                                                                                                                                                                       | 36              |

|     |                                                                                                                                                                                                                                      |                 |

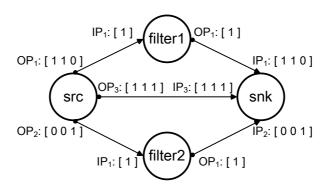

| 3.1 | CSDF graph equivalent to the PPN shown in Figure 2.3                                                                                                                                                                                 | 41              |

x List of Figures

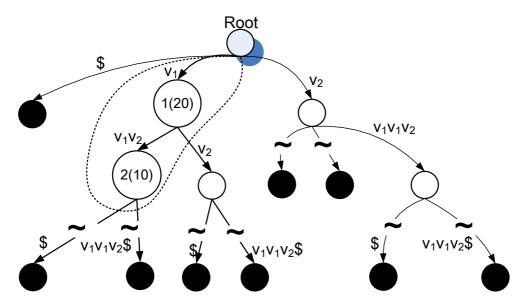

| 3.3        | Suffix tree for the sequence of process variants $S_{snk}$ . The tildes represent the omitted part of the tree                                                                                              | ŀ6       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

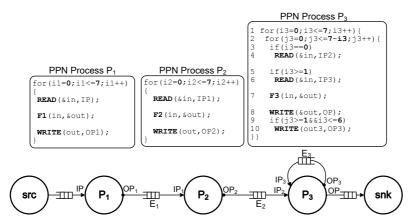

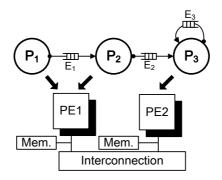

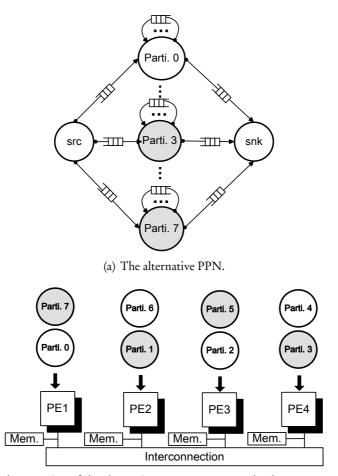

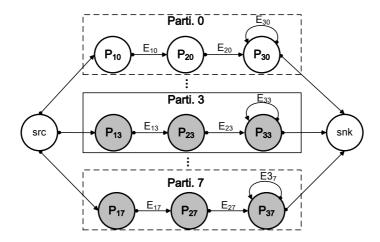

| 4.1<br>4.2 | An example of a PPN and its communication-free partitions 5<br>Mapping of the PPN in Figure 4.1(a) onto 2 PEs achieving the maxi-                                                                           | 54       |

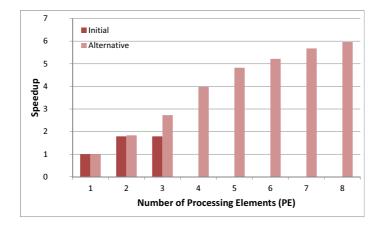

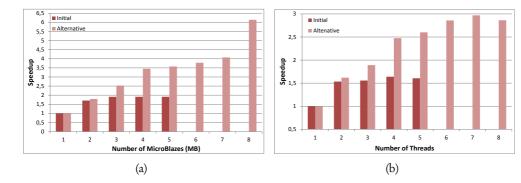

| 4.3        | Performance results of mapping the initial PPN and the alternative                                                                                                                                          | 55       |

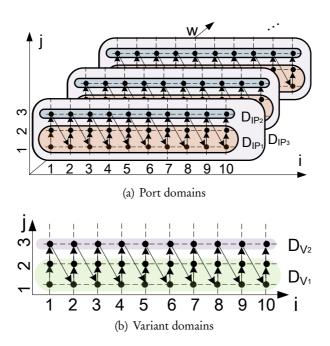

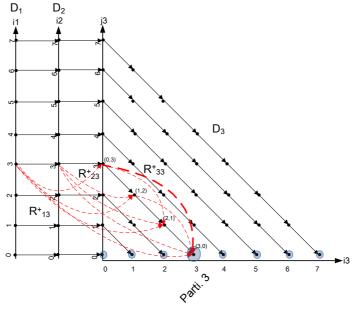

| 4.4        | The PPN in Figure 4.1(a) after communication-free partitioning and                                                                                                                                          | 55       |

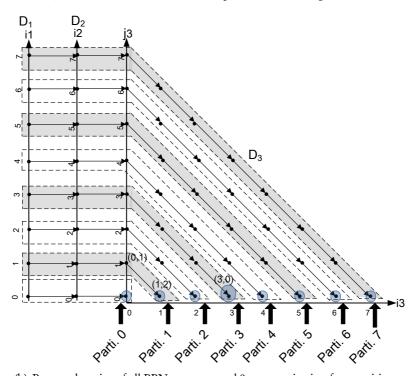

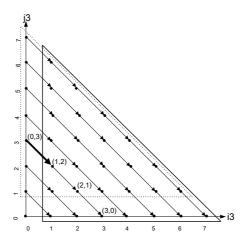

| 4.5        | Domain of PPN process $P_3$ in Figure 4.1(a). The input port domain of $IP_3$ (surrounded by the solid triangle), output port domain of $OP_3$ (surrounded by the dotted triangle), and dependence relation | -6       |

| 1.6        |                                                                                                                                                                                                             | 59<br>51 |

| 4.6<br>4.7 | 0 1                                                                                                                                                                                                         | 51<br>56 |

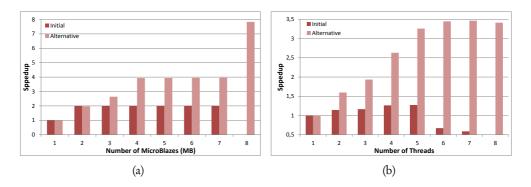

| 4.8        | Performance results of mapping the MJPEG encoder onto (a) FPGA-                                                                                                                                             | )U       |

| 1.0        |                                                                                                                                                                                                             | 70       |

| 4.9        | Performance results of mapping the FM radio application onto (a) FPGA-based MPSoC platforms and onto (b) a desktop multi-core                                                                               | 71       |

|            |                                                                                                                                                                                                             |          |

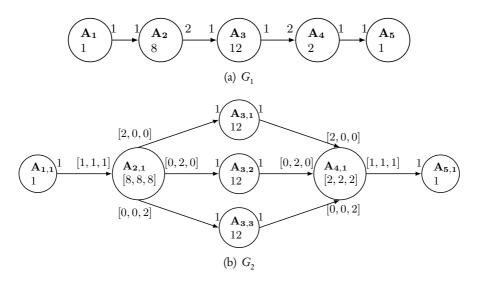

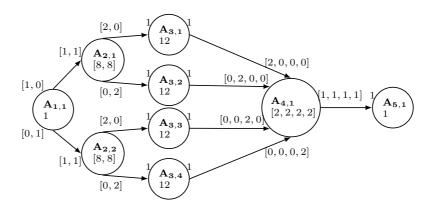

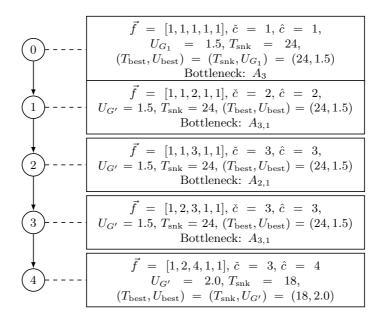

| 5.1        | 7 0 3 7                                                                                                                                                                                                     | 30       |

| 5.2        | $G_3$ : Optimal alternative graph of $G_1$ in Figure 5.1(a) with unfolding factors $f_2 = 2$ , $f_3 = 4$ when scheduled on 2 PEs                                                                            | 35       |

| 5.3        | The list produced by the algorithm for $G_1$ in Figure 5.1(a) on 2 PEs with $\rho = 0.95$                                                                                                                   | 91       |

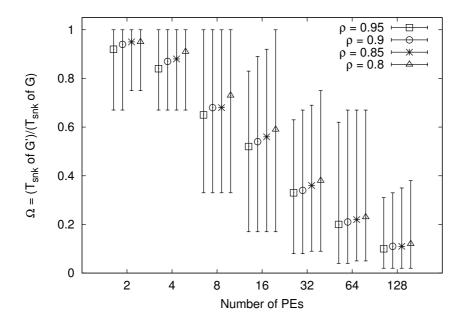

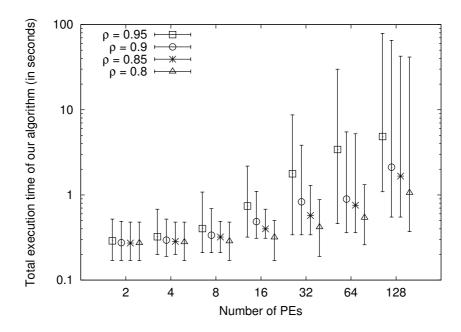

| 5.4        | '                                                                                                                                                                                                           | )4       |

| 5.5        |                                                                                                                                                                                                             | )5       |

| 5.6        | An example of an individual. The first replica of $A_1$ is allocated on                                                                                                                                     |          |

|            | ^                                                                                                                                                                                                           | 96       |

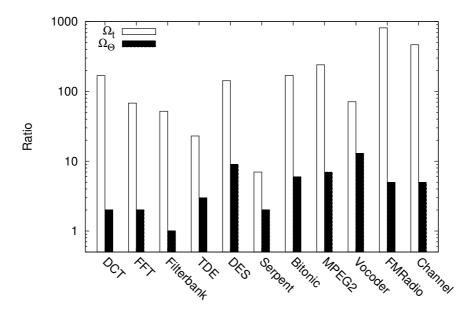

| 5.7        | The ratios of total execution time $\Omega_t$ and total code size $\Omega_\Theta$ for GA                                                                                                                    | 98       |

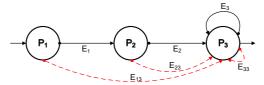

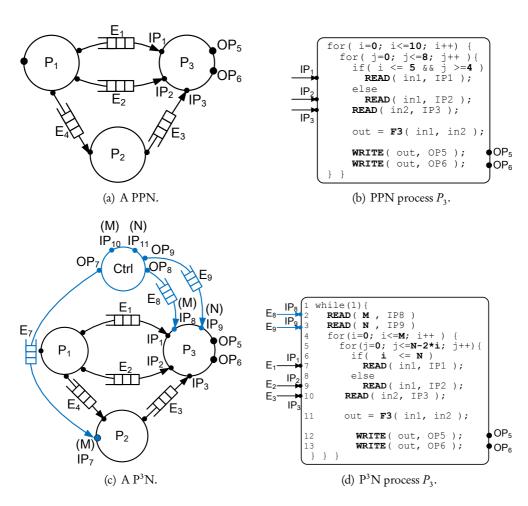

| 6.1        | Comparsion between a PPN and a P <sup>3</sup> N                                                                                                                                                             | 12       |

| 6.2        | Control process and evaluation function                                                                                                                                                                     |          |

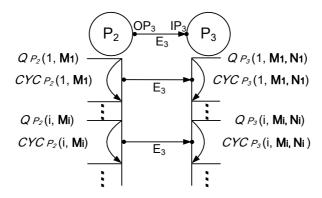

| 6.3        | Consistent execution of process $P_2$ and $P_3$ w.r.t. edge $E_3$                                                                                                                                           |          |

| 6.4        | Which combinations $(M, N)$ do ensure consistency of $P^3N$ ? 10                                                                                                                                            |          |

| 6.5        | Two alternatives of Function Check in Figure 6.2(b)                                                                                                                                                         |          |

List of Figures xi

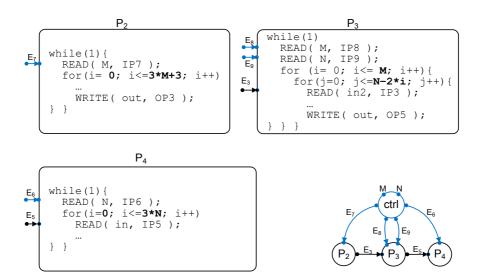

| 6.6  | P <sup>3</sup> N of our experiment                                           |

|------|------------------------------------------------------------------------------|

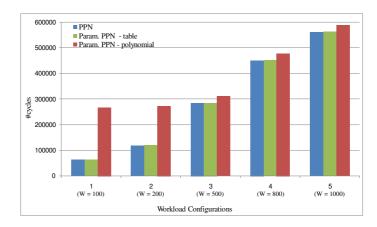

| 6.7  | Performance results of PPN and P <sup>3</sup> N implementations              |

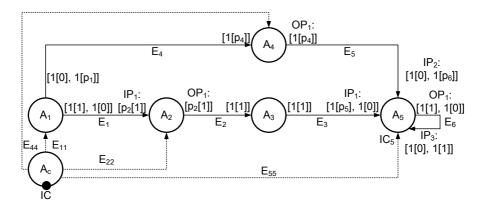

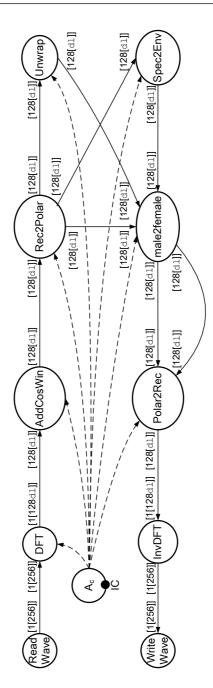

| 7.1  | An example of MADF graph $(G_1)$                                             |

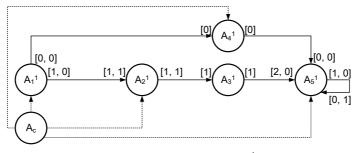

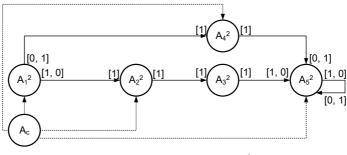

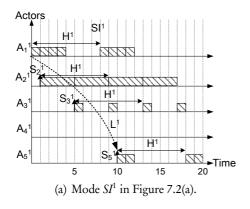

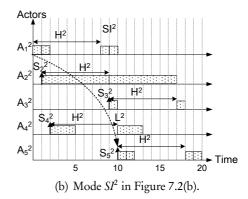

| 7.2  | Two modes of the MADF graph in Figure 7.1                                    |

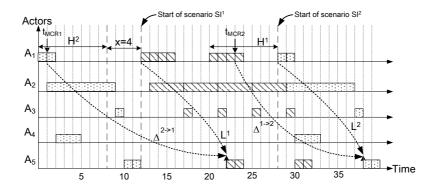

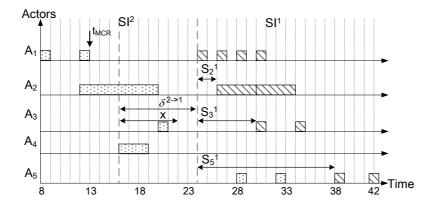

| 7.3  | Execution of two iterations of both modes $SI^1$ and $SI^2$ under self-      |

|      | timed scheduling                                                             |

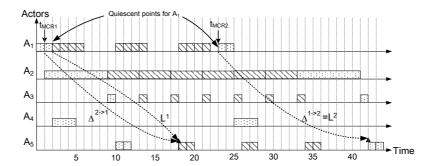

| 7.4  | An execution of $G_1$ in Figure 7.1 with two mode transitions under          |

|      | the ST transition protocol. $MCR1$ at time $t_{MCR1}$ denotes a transition   |

|      | request from mode $SI^2$ to $SI^1$ , and $MCR2$ at time $t_{MCR2}$ denotes a |

|      | transition request from mode $SI^1$ to $SI^2$                                |

| 7.5  | An illustration of the Maximum-Overlap Offset (MOO) calculation. 128         |

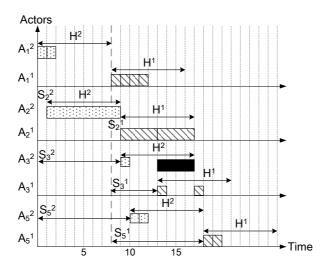

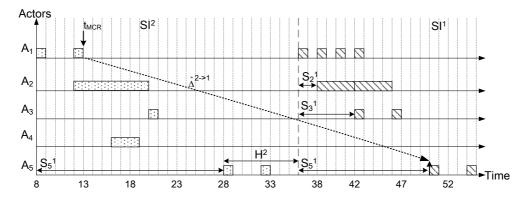

| 7.6  | The execution of $G_1$ with two mode transitions under Maximum-              |

|      | Overlap Offset (MOO) protocol                                                |

| 7.7  | Upper bounds of earliest starting times for transition from mode $SI^2$      |

|      | to $SI^1$                                                                    |

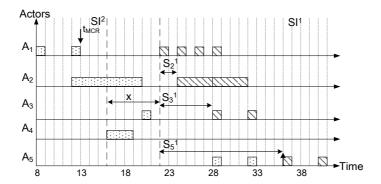

| 7.8  | Earliest starting times for transition from mode $SI^2$ to $SI^1$ with the   |

|      | MOO protocol                                                                 |

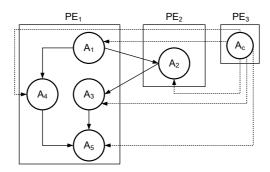

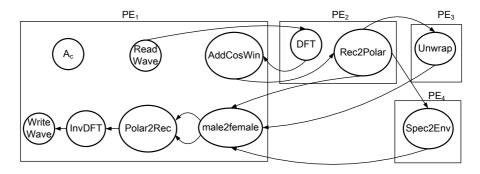

| 7.9  | Allocation of all MADF actors in Figure 7.1 to 3 PEs 136                     |

| 7.10 | Earliest starting times for transition $SI^2$ to $SI^1$ on 2 PEs shown in    |

|      | Figure 7.9                                                                   |

| 7.11 | MADF graph of Vocoder                                                        |

| 7.12 | Allocation of dataflow actors of Vocoder to 4 PEs. The control edges         |

|      | are omitted to avoid cluttering                                              |

## **List of Tables**

| 1.1<br>1.2 | Processing requirements for video decoding (taken from [19]) 3<br>Processing requirements for image processing (taken from [43]). All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2        | applications are assumed to operate at 24 FpsFrame per second 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1        | Mathematical notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.2        | Polyhedral notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3        | Data flow notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.4        | Notations for HRT scheduling of CSDF MoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.1        | Additional notations used in Chapter 3 besides the ones introduced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | in Chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2        | Consumption/production sequences for actor snk in Figure 3.1 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.3        | Characteristics of benchmarks and running times to derive their                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | corresponding CSDF graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4        | Execution times of the phases in the Daedalus <sup>RT</sup> flow for three streaming applications on a single MPSoC platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | or words approximation of words and a province of the second of the seco |

| 4.1        | Execution time on benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1        | Additional notations used in Chapter 5 besides the ones introduced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | in Chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.2        | Benchmark characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.3        | Parameters for the genetic algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.1        | Additional notations used in Chapter 7 besides the ones introduced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | in Chapter 2116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.2        | Mapping relation $M_2$ for actor $A_2$ in Figure 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.3        | Function $MC_5$ defined for actor $A_5$ in Figure 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.4        | Actor parameter for $G_1$ in Figure 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.5        | WCETs of all actors in Vocoder (in clk.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | List of Tables |

|-----|----------------|

| XIV |                |

|     |                |

|     |                |

| 7.6 | Performance results of four modes of Vocoder in the steady-state. | <br>143 |

|-----|-------------------------------------------------------------------|---------|

| 7.7 | Performance results for all mode transitions of Vocoder           | <br>144 |

### **Chapter 1**

#### Introduction

EMBEDDED systems are an essential part of our lives and exist in a wide variety. In 2010, more than 15 billion embedded systems were sold globally [5]. The market for embedded systems was \$113 billion [17]. This market has exhibited steady growth at a compound annual growth rate of 7% for the past 5 years.

An embedded system [84] is an information processing system embedded into devices, products or other systems, for instance mechanical or electrical systems. Different from servers or desktop PCs, embedded systems are often application domain specific and perform certain specific functions tightly coupled to their environment. Such systems can be hidden inside small and simple entities such as digital watches and traffic lights. They can be also a part of large and complex systems, such as Mars Exploration Rover [9].

Embedded streaming systems are an important class of embedded systems, which are specifically designed to process *streaming applications*. A streaming application [59] is a software program that processes large volume of continuous data streams in short periods of time. Typically, the same operation is performed on large set of data items in the stream. Therefore, there is little control flow between processing different data items. Each data item has short life time and is discarded after being processed. This type of applications is ubiquitous in telecommunications, health-care, transportation, retail, science, security, emergency response, and finance. This thesis focuses on those streaming applications that are commonly used in embedded systems. Figure 1.1 shows three popular streaming applications widely used in our daily lives on mobile phones.

Figure 1.1: Three examples of embedded streaming applications.

#### 1.1 Embedded Streaming System Design

Designing embedded streaming systems is definitely a complex process. It involves three main aspects illustrated in the Y-chart [67], namely target applications, underlying platforms, and used design methodologies. This thesis primarily deals with the aspect of design methodology by proposing several novel techniques and a highly automated design framework. The proposed design techniques are highly optimized towards the target applications and platforms with important design requirements in mind. Therefore, first presenting the desired requirements, target applications, and platforms helps understand better the context and contributions of this thesis.

We first show in Section 1.1.1 that the design requirements for embedded streaming systems in general are more strict than general-purpose computing systems. The design techniques proposed in this thesis focus on an important subset of requirements, namely high throughout and hard real-time guarantees. Fortunately, properties of streaming applications can be well exploited with appropriate design techniques, such that the design requirements are satisfied. In addition, application properties show that modern streaming applications exhibit adaptive behavior that has to be explicitly captured in the design methodology. This is one major topic of this thesis. Therefore, we characterize the target applications in Section 1.1.2. Afterwards, we discuss the state-of-the-art hardware platforms in Section 1.1.3 and aim at understanding the architecture capabilities. Ideally, the proper design techniques should exploit application properties in such a way that matches exactly the underlying architecture capabilities. This reinforces the contributions of this thesis. Based on the application properties and selected architecture, we given an overview of a widely acknowledged design methodology in Section 1.1.4. The techniques developed in this thesis significantly extend and strengthen this design methodology.

| Application        | Resolution | Frame rate | Uncompressed<br>bit rate | Compressed<br>bit rate |

|--------------------|------------|------------|--------------------------|------------------------|

| HD-DVD             | 1920x1080  | 25         | 607 Mbps                 | 8-20 Mbps              |

| HDTV               | 1280x720   | 25         | 607 Mbps                 | 2-8 Mbps               |

| DVD                | 720x576    | 25         | 121 Mbps                 | 1-2 Mbps               |

| Video conferencing | 352x288    | 25         | 30 Mbps                  | 128-1000 Kbps          |

|                    |            |            | 1                        | 1                      |

| Mobile video       | 176x144    | 15         | 9 Mbps                   | 50-1000 Kbps           |

Table 1.1: Processing requirements for video decoding (taken from [19]).

| Application       | Resolution | Uncompressed | Compressed |

|-------------------|------------|--------------|------------|

|                   |            | bit rate     | bit rate   |

| Projection        | 1280x720   | 350 Mbps     | 17.5 Mbps  |

| Electronic Cinema |            |              |            |

| Production HDTV   | 1920x1080  | 995 Mbps     | 140 Mbps   |

| Projection        | 4096x2048  | 6040 Mbps    | 450 Mbps   |

| Digital Cinema    |            |              | -          |

| Production        | 4096x3112  | 11000 Gbps   | 2200 Mbps  |

| Digital Cinema    |            |              |            |

Table 1.2: Processing requirements for image processing (taken from [43]). All applications are assumed to operate at 24 FpsFrame per second.

#### 1.1.1 Design Requirements

Requirements referred in this section are non-functional ones, such as performance, timing predictability, thermal aspects [60], security [69], and reliability [128]. The functional requirements such as deadlock-free execution are implicit. This thesis addresses the requirements of high performance and timing predictability.

Embedded streaming systems are expected to have high performance. Sometimes high performance is used interchangeably with high throughput. System throughput is a performance metric which denotes the average number of output data produced by the system per time unit. In general, a system with high throughput is referred to be *fast*. A Digital Video Broadcasting-Handheld (DVB-H) receiver found in mobile devices is a typical embedded streaming system with a certain throughput requirement. Unable to satisfy the throughput requirement results in the videos in slow motion and greatly degrades the user experience. In the video processing domain, the requirements of processing power has also increased drastically as screen resolution increases. Table 1.1 shows processing requirements for different resolutions. The state-of-the-art mobile phones, such as Samsung S4 [12], already have screens with the HD-DVD resolution. From the 5th column in Table 1.1, it

should be clear that designing embedded video streaming system that satisfies the HD-DVD resolution poses a huge challenge. Image processing applications also require high throughput. Table 1.2 shows the processing requirements of different image processing applications used for digital and electronic cinema. The extreme high data rates clearly exceed the processing capacity of conventional embedded streaming systems. For the wireless communication, the requirements have significantly evolved over generations. The 3G standard targets 2 Mbps multimedia service including voice, video, and wireless Internet access. In contrast, it has been proposed in the 4G standard to increase the bandwidth of 100 Mbps or even 1 Gbps.

Besides high performance requirements, many embedded streaming systems pose hard real-time (HRT) requirements. In a HRT system [33], each application in the system has a deadline to indicate the maximum time within which the application must complete its execution. Missing any deadline may cause catastrophic consequence on the system. As noted in [33], a HRT system does not necessarily need to have high throughput requirements. Instead, the timing predictability is the major concern of the HRT system. That is, e.g., if a video conferencing system is guaranteed to produce a decoded video within 1 hour, this system still can be called a HRT system. Of course, this guarantee may not be useful in practice because the latency of producing an output is beyond being acceptable. For a realistic embedded streaming system, HRT constraints often come together with high throughput requirements. For instance, a collision avoidance system in the automotive or avionics domain is such an example. Processing input frames must be completed within a tight deadline. Missing the deadline will lead to catastrophic consequence for the vehicles, for instance potential collision to obstacles. At the same time, it has been reported in [6] that these algorithms require approximately 170 million calculations for each frame update, with the expectation of being executed on up to 64 processors.

#### 1.1.2 Application Characterization

Although the requirements presented in Section 1.1.1 seem strict, streaming applications often contain ample amount of parallelism which can be exploited to satisfy the requirements. Therefore, a characterization of the application properties is needed, which heavily influences and motivates the solutions proposed in this thesis. In this section, streaming applications from different domains are characterized in terms of availability of parallelism and its different forms, computation and data communication characteristics, and adaptive behavior. The selected application domains contain those that are commonly used in embedded system, including video processing, wireless communication, and image processing/computer vision. Below we start by defining different forms of parallelism.