# Parallelizing Dynamic Sequential Programs using Polyhedral Process Networks

Dmitry Nadezhkin

# Parallelizing Dynamic Sequential Programs using Polyhedral Process Networks.

#### **PROEFSCHRIFT**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van de Rector Magnificus prof. mr. P.F. van der Heijden, volgens besluit van het College voor Promoties te verdedigen op donderdag 20 december 2012 klokke 10:00 uur

door

Dmitry Nadezhkin geboren te Arzamas-16, USSR in 1981

#### Samenstelling promotiecommissie:

promotor Prof.dr.ir. Ed F. Deprettere Universiteit Leiden co-promotor Dr.ir. Todor Stefanov Universiteit Leiden

overige leden: Prof.dr. Albert Cohen INRIA, Paris, France

Prof.dr. Marco Bekooij Universiteit van Twente Dr. Andy D. Pimentel Universiteit van Amsterdam

Prof.dr. Joost Kok Universiteit Leiden Prof.dr. Harry Wijshoff Universiteit Leiden

Parallelizing Dynamic Sequential Programs using Polyhedral Process Networks Dmitry Nadezhkin. Thesis Universiteit Leiden. - With ref. - With summary in Dutch ISBN 978-90-9027264-1

Copyright © 2012 by Dmitry Nadezhkin, Leiden, The Netherlands. All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in the Netherlands

To my parents Maria Alexandrovna and Alexander Trofimovich; and my Masha

# Contents

| 1 | Intr | ntroduction 1                                                                                             |    |  |  |  |

|---|------|-----------------------------------------------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Automatic Derivation of Polyhedral Process Networks                                                       | 3  |  |  |  |

|   |      | 1.1.1 Dependence Analysis                                                                                 | 4  |  |  |  |

|   |      | 1.1.2 Linearization                                                                                       | 7  |  |  |  |

|   | 1.2  | Problem statement                                                                                         | 9  |  |  |  |

|   | 1.3  | Motivation and challenges                                                                                 | 11 |  |  |  |

|   | 1.4  | Research Contributions                                                                                    | 14 |  |  |  |

|   | 1.5  | Related Work                                                                                              | 14 |  |  |  |

|   | 1.6  | Dissertation Outline                                                                                      | 17 |  |  |  |

| 2 | Bac  | kground                                                                                                   | 19 |  |  |  |

|   | 2.1  | Preliminaries                                                                                             | 20 |  |  |  |

|   |      | 2.1.1 Polyhedral Model                                                                                    | 20 |  |  |  |

|   | 2.2  | The Program Model                                                                                         | 22 |  |  |  |

|   | 2.3  | Polyhedral Process Networks                                                                               | 24 |  |  |  |

|   | 2.4  | Exact Array Dataflow Analysis                                                                             | 26 |  |  |  |

|   | 2.5  | Fuzzy Array Dataflow Analysis                                                                             | 28 |  |  |  |

|   | 2.6  | Communication model identification in PPNs derived from static programs                                   | 32 |  |  |  |

| 3 |      | omated Generation of Polyhedral Process Networks from<br>ne Nested-Loop Programs with Dynamic Loop Bounds | 35 |  |  |  |

|       | 0 1     |    |

|-------|---------|----|

| V111  | Content | tc |

| A TIT | Conten  | u  |

|   | 3.1  | Solution                                                         | on Overview                                                                            | 36 |  |  |

|---|------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|----|--|--|

|   | 3.2  | Step 1                                                           | (Dynloop-to-WDP)                                                                       | 37 |  |  |

|   | 3.3  | Step 2                                                           | (FADA analysis)                                                                        | 38 |  |  |

|   |      | 3.3.1                                                            | Initial dSAC                                                                           | 39 |  |  |

|   | 3.4  | Step 3                                                           | (Control arrays)                                                                       | 40 |  |  |

|   |      | 3.4.1                                                            | Local control arrays                                                                   | 41 |  |  |

|   |      | 3.4.2                                                            | Global control arrays                                                                  | 42 |  |  |

|   | 3.5  | Step 4                                                           | (PPN generation)                                                                       | 43 |  |  |

|   |      | 3.5.1                                                            | Topology creation of a PPN (substep 1)                                                 | 44 |  |  |

|   |      | 3.5.2                                                            | Internal code structure generation (substep 2)                                         | 44 |  |  |

|   |      | 3.5.3                                                            | Linearization (substep 3)                                                              | 45 |  |  |

|   | 3.6  | Calcul                                                           | lation of deadlock-free buffer sizes                                                   | 46 |  |  |

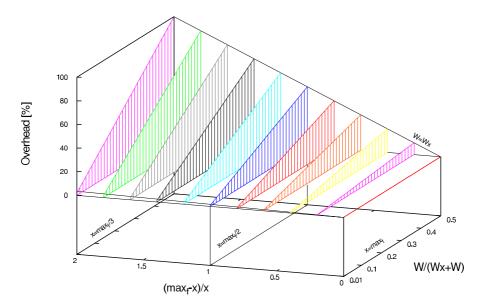

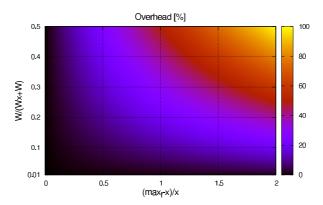

|   | 3.7  | Overh                                                            | ead Analysis                                                                           | 49 |  |  |

|   | 3.8  | Discus                                                           | ssion and Summary                                                                      | 52 |  |  |

|   |      |                                                                  |                                                                                        |    |  |  |

| 4 |      |                                                                  | l Generation of Polyhedral Process Networks from<br>ted-Loop Programs with While-loops | 55 |  |  |

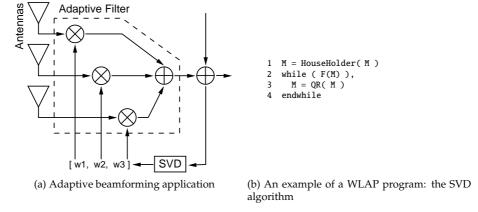

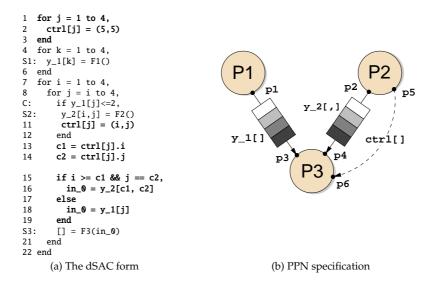

|   | 4.1  |                                                                  | ating example                                                                          | 56 |  |  |

|   | 4.2  |                                                                  | on Overview                                                                            |    |  |  |

|   | 4.3  |                                                                  | (FADA analysis)                                                                        |    |  |  |

|   | 4.4  | •                                                                | (Initial dSAC)                                                                         | 60 |  |  |

|   | 4.5  | _                                                                | (Control variables)                                                                    | 62 |  |  |

|   |      | 4.5.1                                                            | Additional control variables                                                           |    |  |  |

|   | 4.6  | Step 4                                                           | (PPN generation)                                                                       | 64 |  |  |

|   |      | 4.6.1                                                            |                                                                                        | 65 |  |  |

|   |      | 4.6.2                                                            | Substep 2: Code generation                                                             | 66 |  |  |

|   |      | 4.6.3                                                            | Substep 3: Linearization                                                               | 67 |  |  |

|   |      | 4.6.4                                                            | Substep 4: Implementation of a while-loop's iterator $w$                               | 68 |  |  |

|   | 4.7  |                                                                  | ssion and Summary                                                                      | 69 |  |  |

|   |      |                                                                  |                                                                                        |    |  |  |

| 5 |      | ntifying Communication Models in Polyhedral Process Networks de- |                                                                                        |    |  |  |

|   | rive | a trom                                                           | Dynamic Programs                                                                       | 71 |  |  |

| C  | onten      | ts                           | ix  |

|----|------------|------------------------------|-----|

|    | 5.1<br>5.2 | Rationale                    | 73  |

|    | 5.3        | Discussion and Summary       |     |

| 6  | •          | erimental Studies            | 79  |

|    | 6.1<br>6.2 | Low Speed Obstacle Detection |     |

| 7  |            | nmary and Conclusions        | 87  |

| Bi | bliog      | graphy                       | 91  |

| In | dex        |                              | 97  |

| A  | cknov      | wledgments                   | 99  |

| Sa | men        | vatting                      | 101 |

| Cı | ırricı     | ılum Vitae                   | 103 |

| Li | st of      | Publications                 | 105 |

# Introduction

In the work entitled "Dialectics of Nature" Friedrich Engels (1883) formulated the law which can describe the universal law of nature, the material world and human society. According to the law the quantitative changes in a system eventually pass into qualitative changes. Not surprisingly, this law could also explain the advances that have been taking places during the last decade in the computer industry.

The quantitative advances in the computer industry were predicted and formalized by the Moore's law. The law predicted the doubling of transistor densities every 18 to 24 months. Coupled with the increase of processor frequencies these led manufacturers to produce faster and more powerful processors every year. But these advances inevitably came to their end at some point in time. Growing disparity of speed between the CPU and the memory could not further improve the speed of computation. Additionally, increasing density of transistors leads to prohibitively high levels of power consumption, heat and power leakage. This is a prove that quantitative advances in hardware technologies could not be further a driving force in the computer industry.

To overcome these problems chip manufacturers have moved from single processor systems to multiprocessor or parallel systems. This allows to run processors on lower frequencies and combine general purpose processors with dedicated processors leading to heterogeneous systems with more optimized usage of transistors. The world of computers moved from sequential computing to parallel computing, or, in other words, the quantitative advances have been transformed into qualitative advances.

Although, we are witnessing the emergence of parallel (multi-core and multi-processor) systems in all markets: from general-purpose computing to embedded systems, e.g., multimedia systems, game consoles and all sorts of mobile devices, the transition from sequential to parallel computing is far from trivial. To satisfy emerging applications requirements, the multiprocessor embedded systems must be pro-

grammed in a way that the available parallelism is revealed and exploited efficiently. However, the programming of a multiprocessor system is a challenging, error-prone, and time consuming task as it involves the partitioning of programs, and consequently, synchronization of different program partitions.

In recent years, a lot of attention has been paid to the design of parallel systems. However, insufficient attention has been paid to the development of concepts, methodologies, and tools for efficient programming of such systems. Therefore, the programming still remains a major difficulty and challenge [1]. Today, system designers experience significant difficulties in programming parallel systems because the way an application is specified by an application developer, typically as a *sequential* program using a *sequential* model of computation (MoC), does not match the way multiprocessor systems operate, i.e., multiple cores run (possibly) in parallel.

If an application is specified using a *parallel* MoC, then the mapping of this application onto a multiprocessor system can be done in a systematic and transparent way by using a disciplined approach [2]. Using a parallel MoC facilitates the programming of parallel multiprocessor systems because a parallel MoC makes the parallelism available in an application and the communication between the application tasks explicit. Unfortunately, specifying an application using a parallel MoC is very difficult as the application developers i) have to be familiar with a particular parallel MoC; ii) have to study the application in order to identify possible parallelism that is available and to reveal it by using the parallel model.

To relieve the designer from all these difficulties, the *pn* compiler [3] was introduced. It implements techniques for automated parallelization of static affine nested loop programs (SANLP) written in a subset of *C*-language equivalent to the program model presented in [4] into input-output equivalent Polyhedral Process Network (PPN) descriptions. In the *pn* partitioning strategy, a process is created for every statement and function call found in the top-level of the program. In this way, the designers have control over the granularity of the created partitions.

```

1 parameter N 10 100;

2 for j = 1 to 6*N-3,

3    A[j] = Func1()

4 endfor

5 for j = 0 to N,

6    for i = j to 3*j-2,

7     if( i+j < 4*N-6 )

8         A[i] = Func2( A[2*i-1], A[2*i+1] )

9         endif

10         Func3( A[i] )

11         endfor

12 endfor</pre>

```

Figure 1.1: Pseudo code of a SANLP.

An example of a SANLP is given in Figure 1.1. In this and following figures in this dissertation, the examples will be given in pseudo code which semantics is equivalent to the semantics of the program model presented in [4]. We decided to use the pseudo code syntax instead of *C*-language syntax in order to avoid syntax clutter

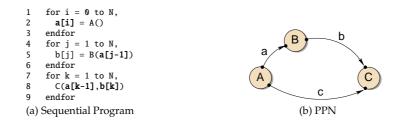

of C-language and emphasize that input programs considered in this dissertation are not language specific. A SANLP in Figure 1.1 consists of a set of statements and function calls, each possibly enclosed in loops and/or guarded by conditions. The loops do not have to be perfectly nested. All lower and upper bounds of the loops as well as all expressions in conditions and array accesses have to be affine functions of enclosing loop iterators and static parameters. The parameters are symbolic constants, i.e., their values can not change during the execution of the program. Rather, parameter values determine different program instances. In addition, data communication between function calls must be explicit. For example, see function Func2() at line 8 which accepts 2 elements of array A as input arguments. Providing just a pointer to array A in this case is not allowed. The above restrictions allow a compact mathematical representation of a SANLP using the well-known polyhedral model [5]. The SANLPs can be converted in an automated way into Polyhedral Process Networks [3].

The target Polyhedral Process Networks (PPNs) [6] is a special case of the Kahn Process Networks (KPNs) [7] model of computation. A PPN consists of concurrent autonomous processes that communicate data in a point-to-point fashion over bounded FIFO channels using a blocking read/write on an empty/full FIFO as synchronization mechanism. In addition, everything about the execution of a PPN is known at compile-time. The latter enables techniques for modeling, analysis, and SW/HW synthesis in a systematic and automated way, and allows the calculation of buffer sizes that guarantee deadlock-free execution. In comparison, computing buffer sizes is not possible for the more general KPN model. We are interested in the process network model because it provides a sound formalism, well suited for capturing and modeling of data-flow dominated applications in the realm of multimedia, imaging, and signal processing, that naturally contain tasks communicating via streams of data. Moreover, it has been already shown that process networks allow effective and efficient mappings of streaming applications to certain parallel execution platforms [8–13].

### 1.1 Automatic Derivation of Polyhedral Process Networks

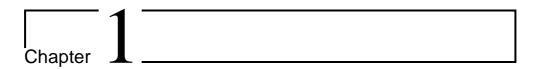

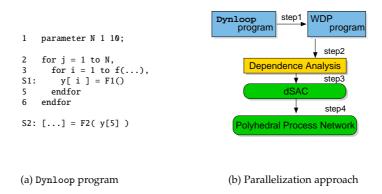

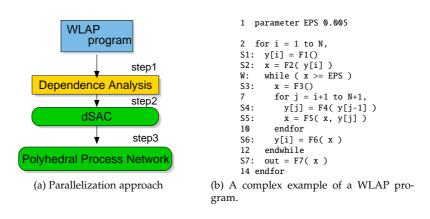

In this section we briefly recall the systematic parallelization approach [14] used to derive Polyhedral Process Network from static sequential programs. This overview will help to understand the contributions of this dissertation.

The approach is illustrated in Figure 1.2(b). It starts with an application written as a sequential program similar to the one depicted in Figure 1.1. In many cases completely sequential execution can be relaxed without compromising the correctness of the execution. That is, the order of the program statements can be rearranged without changing the program functionality under the ordering constraints. In fact, the possibility to rearrange statements is actually the possibility to execute them in parallel. Ordering constraints are dictated by the data dependency relations existing in the sequential program. Therefore, the first main step of the parallelization

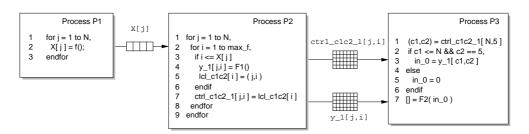

Figure 1.2: An example of a Static Affine Nested Loop Program, approach that translates SANLPs into PPNs, intermediate representation Polyhedral Reduced Dependence Graph and resulting PPN.

approach depicted in Figure 1.2(b) is to perform *data dependence* analysis between evaluations of statements. The analysis helps to extract the dependent memory accesses and present an initial program in a form where data dependencies are made explicit. Thus, the initial program is translated into the Single Assignment Code (SAC) [4] form or its analogous form called Polyhedral Reduced Dependence Graph (PRDG) [15] which is a compact mathematical representation of the dependency relations in terms of polyhedra. In PRDG the nodes represent statements of the initial program and the edges represent data dependencies. The PRDG model still exploits (multi-)dimensional arrays for data communication. However, the target model, Polyhedral Process Networks, requires FIFO channels as communication medium. Therefore, another step is needed that converts multi-dimensional memory accesses into managed dataflow over FIFO queues. This step called *Linearization* constitutes the second main step of the approach shown in Figure 1.2(b). In the following, we give more detailed overview of these steps.

#### 1.1.1 Dependence Analysis

The goal of the *Dependence Analysis* step is to determine if evaluation of a statement depends on evaluation of other statements and to find these evaluations. For example, in the SANLP program depicted in Figure 1.2(a), the purpose of the dependence analysis is to find whether statement *S*3 depends on statements *S*1 or *S*2 via array y and at which particular iterations. Or in other words, for every element of array y read at a given iteration of statement *S*3, the dependence analysis finds which statement, *S*1 or *S*2, and at which iteration it writes data to the given array element. The most relevant algorithm to perform the analysis is the Exact Array Dataflow Anal-

1.1 PPN derivation 5

ysis (EADA) [4]. This algorithm considers all pairs of statements where one writes and the other reads from possibly the same memory addresses. For each pair a special system of linear (in)equalities is built. This system defines in an affine form the conditions when two statements are data dependent. The formal definition of this system of linear (in)equalities will be given in Chapter 2. For example, Table 1.1 depicts two systems of linear inequalities  $\mathbf{Q}_{S1S3}((i_3,j_3))$  and  $\mathbf{Q}_{S2S3}((i_3,j_3))$  for pairs S1S3 and S2S3, respectively. Note that with  $(i_3,j_3)$ , iteration vector (i,j) of statement S3 is denoted. Similarly, with  $(i_2,j_2)$  and k iteration vectors of statements S1 and S3 are denoted, respectively.

The meanings of constraints (c1)–(c3) are the following. The first constraint (c1) states that the source iteration has to exist, i.e., it has to belong to the iteration domain of a potential source statement. The constraint (c2) specifies that if there is a dependency between evaluation of two statements, both have to access the same array element. The (c3) constraint determines an order of operations, i.e., writing to the array cell in one statement should be performed *before* reading from the same array cell in the other statement. The order of operations is defined by the sequential order of the initial program.

| $\overline{\mathbf{Q}_{\mathrm{S1S3}}((i_3,j_3))}$ | $\mathbf{Q}_{\mathrm{S2S3}}((i_3,j_3))$                               |      |

|----------------------------------------------------|-----------------------------------------------------------------------|------|

| $1 \le k \le M$                                    | $1 \le i_2 \le N \land i_2 \le j_2 \le M \land $ $j_2 \le 2$          | (c1) |

| $k = j_3$                                          | $j_2 = j_3$                                                           | (c2) |

| true                                               | $\langle S2, (i_2, j_2) \rangle \prec \langle S3, (i_3, j_3) \rangle$ | (c3) |

Table 1.1: Systems used in dependence analysis between statements S1S3 and S2S3 in the program shown in Figure 1.2(a).

Having these systems formulated, the data dependence algorithm finds the lexicographical maximum between all vectors satisfying the systems. Finding a lexicographical maximum means to solve the Parametric Integer Linear Problems (PILPs), where **objective** is the lexmax function **subjected to** conditions stated by systems  $\mathbf{Q}()$ . The solution to find the maximum point for a given convex domain defined by the systems is based on the dual simplex method [16] that is implemented in open-source libraries such as isl [17], Parma Polyhedral Library [18], and PIPLib [19]. Finally, the source operation for the data read by statement S3 is:

if

$$j_3 \leq 2$$

then  $\langle S2, (i_3, j_3) \rangle$  else  $\langle S1, (j_3) \rangle$ . (1.1)

The solution above shows that the source of the data for statement S3 of the program in Figure 1.2(a) can be from two different statements. The source is statement

S1 when the iterator j of S3 is greater than 2. Otherwise, the source is statement S2. The result of the analysis forms the dependency relations between iterations of statements writing/reading to/from the array.

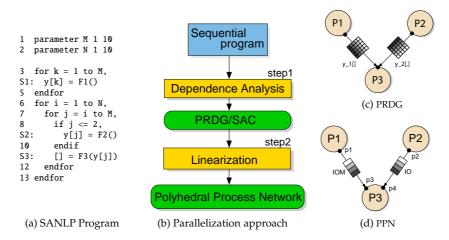

Figure 1.3: Single Assignment Code form and data dependencies relations in the program depicted in Figure 1.2(a).

For illustrative purposes, the same result can be depicted in a graphical form as shown in Figure 1.3(b). In the figure the dependencies are found for values of program's parameters M and N equal to 4. The coordinate systems show the iteration domain of statements *S*1, *S*2 and *S*3. The points on the coordinate systems designate the evaluations of statements *S*1, *S*2 and *S*3, and the arrows reflect the data dependency relations.

Based on the results of the dependence analysis, the initial sequential program can be translated into the Single Assignment Code (SAC) form which is introduced in [4]. The SAC program is functionally equivalent to the initial program, with the difference that every variable is written exactly once. The latter ensures that all data dependencies are explicitly revealed and respected. The SAC form of the initial program shown in Figure 1.2(a) is illustrated in Figure 1.3(a). In this SAC program, the original array y[] is substituted with multi-dimensional dedicated arrays y\_1[] and y\_2[,], and control at lines 6 and 9 is added in order to respect the original data dependency relations. The SAC form of the initial program is easily convertible to the Polyhedral Reduced Dependence Graph (PRDG) [15]. The PRDG is a graph where nodes represent computation and edges represent communication. Nodes communicate point-to-point via unique dedicated multi-dimensional arrays that respect the original data dependencies. An example of a PRDG derived from the program shown in Figure 1.2(a) is illustrated in Figure 1.2(c). It consists of three processes that correspond to the statements of the SAC program shown in Figure 1.3(a), and two arrays that correspond to the arrays y\_1[] and y\_2[,] of the same program. It is important to note that rather than introducing a node for each iteration of a statement in a SAC, in PRDG, a node specifies a regular set of all iterations of a statement in a SAC program. This regular set is defined in terms of polyhedra. The definition of polyhedra and its relation to affine nested loop programs will be given 1.1 PPN derivation 7

Figure 1.4: Types of communication models in a PPN.

#### in Chapter 2.

To summarize, the *Data Dependence* step of the parallelization approach shown in Figure 1.2(b) translates the initial sequential program into its functionally equivalent PRDG which specifies a program in terms of topology, behavior and geometry. The geometrical polyhedral specification makes this model useful for different transformations [20]. The explicit separation between communication, computation and geometrical characterization allows for translation from communication via shared memory to FIFO channels which constitutes the *Linearization* step of the parallelization approach.

#### 1.1.2 Linearization

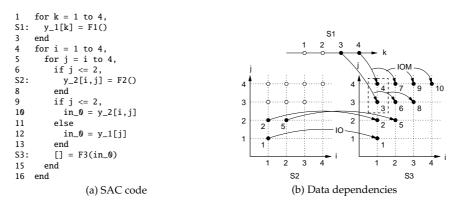

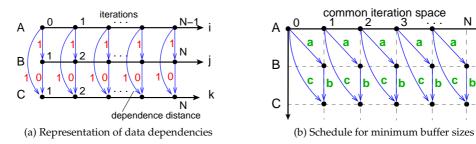

In a PRDG, the storage structure of the initial program is transformed such that each Producer/Consumer (P/C) pair of nodes communicates over dedicated multidimensional memory arrays as shown in Figure 1.2(c). However, in the target PPN model, communication is required to be done via FIFO channels instead of multidimensional arrays because, for example, such communication allows for simple implementation of data streams in software and hardware. The *Linearization* step of the parallelization approach replaces all such multi-dimensional arrays with FIFO channels. However, due to the particular way the data flows from a Producer node to a Consumer node, mapping array communication onto FIFO channels requires complex address generators, especially if the arrays have multiple dimensions. Therefore, the Linearization also solves the Communication Model Identification (CMI) problem, which investigates communication characteristics of each P/C pair of nodes in a PRDG. The CMI problem is an optimization problem that allows to identify communication behavior of a FIFO channel that is cheaper for realization. We explain this in the following example.

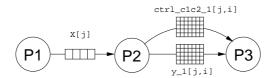

Every FIFO channel implemented as a point-to-point communication has one Producer and one Consumer node or processes, thereby forming a Producer/Consumer pair (P/C pair). An example of two P/C pairs P1/P3 and P2/P3 is shown in Figure 1.2(d).

In any point-to-point communication, the firings of the Producer process generate data tokens in a certain order. We call it the production order. The tokens are sent to the Consumer process over the FIFO channel. In order to fire, the Consumer process needs the data tokens in a certain order. We call it the consumption order. When the production and consumption orders are the same, we say that the P/C pair communication is *in-order*. Otherwise, the P/C pair communication is *out-of order*. Consider, for example, Figure 1.4(a). It depicts the Producer and Consumer processes, where the points on the coordinate systems designate the firings of the processes and the arrows reflect the data dependencies between firings. The numbers at the points show the production/consumption orders. Figure 1.4(a) shows that the production order of the Producer process coincides with the consumption order of the Consumer process. This is an example of *in-order* communication in a P/C pair. Similarly, Figure 1.4(c) illustrates that the consumption order of the Consumer is reversed to the production order of the Producer process. This is an example of *out-of-order* communication.

In a P/C pair, it may occur that the Consumer process may need to reuse in future firings a token that has just been received from the Producer process. In such case we say that the P/C pair communication has a *multiplicity*. For example, consider the firing of the Producer and Consumer depicted in Figure 1.4(b). The production and consumption orders are the same, thus, the P/C pair communication is *in-order*. Additionally, we may notice, for example, that the data token needed for firing 3 of the Consumer process, will be needed on firings 6 and 8. Thus, the P/C pair communication has a multiplicity. Likewise, a P/C pair communication may be *out-of-order* and has a *multiplicity*. An example of such P/C pair communication is depicted in Figure 1.4(d). The four different types of P/C pair communication described above, determine four communication models between processes. They are: *in-order* (IO), *out-of-order* (OO), *in-order with multiplicity* (IOM) and *out-of-order with multiplicity* (OOM). The communication of a P/C pair belongs to one of these four types only.

According to the explanations given above, the communication models between nodes formed by statements S1/S3 and S2/S3 in Figure 1.3(b) are IOM and IO, respectively.

1.2 Problem statement

```

1 parameter M 1 10;

1 parameter M 1 10;

1 parameter M 1 10;

2 parameter N 1 10

2 parameter N 1 10

2 parameter N 1 10

for k = 1 to M,

3 for k = 1 to M,

3 for k = 1 to M,

S1: y[k] = F1()

S1: y[k] = F1()

S1: y[k] = F1()

5 endfor

5 endfor

6 for j = 1 to N,

6 for i = 1 to N,

6 for i = 1 to N,

for i = 1 to f(...),

for j = i to M,

S1: y[i] = F1()

if y[j] <= 2,

c:

S1:

y[i] = F1()

8 while (...),

S2: y[i] = F2()

S2:

y[j] = F2()

endfor

endif

10 endfor

endwhile

10

10

S3: [] = F3(y[j])

S3: [] = F3(y[i])

S2: [...] = F2(y[5])

12 endfor

13 endfor

(a) Weakly Dynamic Pro- (b) Affine program with dy- (c) Affine program with while-

gram (WDP).

namic loop bounds (Dynloop). loop (WLAP)

```

9

Figure 1.5: Examples of WDP, Dynloop and WLAP programs. The differences are that in WDP program, there is a dynamic if-condition at line C; in Dynloop, the upper bound of for-loop *i* at line 7 is data-dependent; in WLAP program, the second loop at line 8 is a while-loop.

In order to implement a PPN, all communication models have to be realized over a FIFO channel. The *in-order* models can be implemented with a FIFO in a straightforward way, as the order of writing into the FIFO channel and the order of reading from it are the same. The *out-of-order* models would require a FIFO channel augmented with a controller implementing the reordering. In a similar manner, the models with *multiplicity* would require a FIFO channel with additional memory to store the tokens which will be reused later.

The difference in realization puts the communication models into a hierarchy. The realization of the *OOM* model is the most general, as it is built of all components present in the realizations of the other models. In other words, all P/C pair communication models can be implemented with the realization of the *OOM* model. However, the more general a realization is, the more resources it needs and more run-time overhead is introduced. More importantly, the *IO,OO* and *IOM* communication models might be implemented with simpler realization.

Thus, we see that in order to parallelize a sequential application two important steps, *Dependence Analysis* and *Linearization*, should be addressed.

#### 1.2 Problem statement

Many scientific, matrix computation, and signal processing applications can be specified as static affine nested loop programs (SANLPs), and therefore, the *pn* compiler [3], briefly described in Section 1.1, can be used to derive equivalent parallel PPN specifications. However, many multimedia applications such as MPEG coders/decoders, Smart Cameras, adaptive filters, iterative algorithms, etc. have adaptive

and dynamic behavior which can not be expressed as static programs as SANLPs.

In order to handle such dynamic applications, in this dissertation we address an important question: whether some of the static restrictions of the SANLPs can be relaxed while keeping the ability to perform compile-time analysis and to derive PPNs in an automated way. Achieving this will significantly extend the range of applications that can be parallelized in an automated way.

By studying different dynamic applications we distinguished three relaxations to SANLP programs that would allow one to specify dynamic applications as sequential programs.

#### The first relaxation:

I. dynamic if-conditions are allowed in a program.

An example of an application with this relaxation is depicted in Figure 1.5(a). Note, that the if-statement at line C has a dynamic condition " $y[j] \le 2$ ". This condition is dynamic because it depends on the variable y[j] whose value is determined during program execution. As a real-life example of an application that contains such relaxation, the Motion JPEG (M-JPEG) encoder [21–23] can be considered.

#### The second relaxation:

II. for-loops with dynamic bounds are allowed in a program.

An example of an application with this relaxation is depicted in Figure 1.5(b). Note, that the upper bound of for-loop i at line 7 is an arbitrary function f(...). As an example of a real-life application containing for-loops with dynamic bounds an application from the smart cameras domain called Low Speed Obstacle Detection (LSOD) [24] can be considered. The detailed analysis of this application will be given in Chapter 6.

#### The third relaxation:

III. while-loops are allowed in a program.

An example of an application with this relaxation is depicted in Figure 1.5(c). Note, that the loop at line 8 is a while-loop. An example of a real-life application containing while loop is the application from the signal processing domain called Adaptive Beamforming (AB) [25].

In the rest of this dissertation, a program that contains either of these three relaxation will be called a *dynamic program*.

In [21], the first relaxation has been considered, i.e., how to translate affine nested-loop programs with dynamic if-conditions into input-output equivalent PPNs in

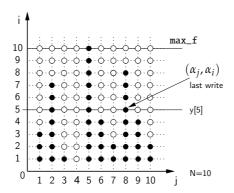

Figure 1.6: Dependency relations in a dynamic program.

an automated way. In this dissertation, we consider the other two more difficult relaxations. Finally, we formulate the problem which is solved in this dissertation:

to develop an automated procedure for translation of affine programs with relaxations II and III into input-output equivalent Polyhedral Process Networks.

## 1.3 Motivation and challenges

The overall challenge of deriving a PPN from a dynamic program is how to deal with uncertainties introduced by the relaxations presented in Section 1.2. Below, we demonstrate that: 1) an exact data dependence analysis (EADA) and *exact* communication model identification (CMI) in PPNs derived from dynamic programs are not possible at compile-time; 2) the existing approach used for PPN derivation presented in Section 1.1 cannot be used to identify communication models and translate dynamic programs into PPNs; 3) nevertheless, at compile-time, for any P/C pair it is possible to identify the most general communication model which can be used to realize all possible data dependency patterns that may occur in different instances of the dynamic program.

Consider, for example, the dynamic program shown in Figure 1.5(a) which contains dynamic relaxation I. The program has a dynamic condition at line C evaluating some run-time data. Depending on the evaluation of the if-condition, either statement S1 or S2 produces the data for every firing of statement S3.

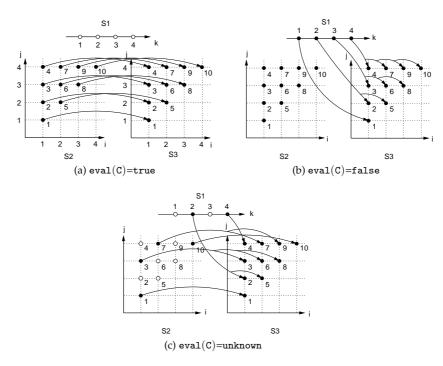

Figure 1.6 depicts data dependency relations between statements S1, S2 and S3 in three instances of this program for M=N=4, where an instance of a dynamic program is an evaluation of the program with a particular input dataset. Figure 1.6 illustrates iteration domains of statements S1, S2 and S3, where the points on the coordinate systems designate the evaluations of statements and the arrows reflect the data dependencies between evaluations. The numbers at the points show the lexicographical order of statement evaluations.

Assume, first, that the condition at line C always evaluates to *true*, and, thus, all the data needed by statement S3 is produced by statement S2 only (see Figure 1.6(a)). The opposite case is when the condition at line C always evaluates to *false*. Depicted in Figure 1.6(b), this time, relations exist between statement S1 and S3 only. In general, however, the result of condition evaluation at line C is arbitrary and unknown at compile-time. An example of this case is shown in Figure 1.6(c). In this case, on some firings, the data needed by statement S3 is produced by statement S1, on other firings by statement S2.

The three examples of data dependency relations illustrated in Figure 1.6 show the difference of dependency patterns between dynamic and static programs. In static programs, different instances of a program correspond to one and the same single dependency pattern which is known at compile-time. In dynamic programs, data dependency patterns correspond to different *instances* of a dynamic program, and are unknown at compile time. This also means that data dependency patterns in a dynamic program cannot be determined at compile-time by the exact array dependence analysis.

We can illustrate the same idea by using the description of the exact dependence analysis presented in Section 1.1.1. Recall, that this analysis constitutes Step 1 of the parallelization approach depicted in Figure 1.2(b). In order to determine data dependency patterns at compile-time the data dependence analysis has to be performed on a initial program. The dependence analysis algorithm builds a system of linear inequalities similar to one shown in Table 1.1. Consider, for example, the dynamic program in Figure 1.5(a), and let us build the system for pair S2S3:

Then, the data dependence algorithm finds the lexicographical maximum between all vectors satisfying the systems by solving Parametric Integer Linear Problems problem. However, in the system shown in Table 1.2 constraint (c1) which specifies the domain of the source iteration is not a convex domain as it contains dynamic if-condition y[j] <= 2. Therefore, the exact data dependence analysis presented in Section 1.1.1 cannot be applicable to dynamic programs.

The same reasoning applies to the dynamic programs with the other two relaxations II and III. Overall, this shows that the approach presented in Section 1.1 cannot handle the dynamic programs shown in Figure 1.5.

| $\mathbf{Q}_{\mathrm{S2S3}}((i_3,j_3))$                               |      |

|-----------------------------------------------------------------------|------|

| $1 \le i_2 \le N \land i_2 \le j_2 \le M \land$                       | (c1) |

| $y[j_2] \le 2$                                                        |      |

| $j_2 = j_3$                                                           | (c2) |

| $\langle S2, (i_2, j_2) \rangle \prec \langle S3, (i_3, j_3) \rangle$ | (c3) |

Table 1.2: The system used to perform exact dependence analysis between statements S2S3 in the program shown in Figure 1.5(a).

The inability to determine the exact data dependency relations in a program makes the exact communication model identification impossible. Nevertheless, still we can analytically identify at compile-time the communication models of a P/C pair in all possible instances of a dynamic program. Based on this information, we can realize the communication of a P/C pair with the most general communication model which implements all possible data dependency relations. For example, we may observe in Figure 1.6 that the production/consumption orders in S1/S3 and S2/S3 pairs are the same. Thus, the communication in all P/C pairs is *in-order*. Moreover, in some program instances a multiplicity in the communication is possible and, according to the realization hierarchy of communication models, the most general model for S1/S3 and S2/S3 pairs is *IOM*. Therefore, we can implement the communication in S1/S3 and S2/S3 pairs as *IOM* model.

In order to solve the problem addressed in this dissertation and formulated in Section 1.2, we split the problem in 2 issues. The first issue is formulated as follows:

• **Issue I**: dynamic programs with the relaxations presented in Section 1.2 require different parallelization approach in translating them into PPNs compared to the approach presented in Section 1.1. Loop iteration domains and the overall dataflow is unknown at compile-time in dynamic programs. [21] considered relaxation I, i.e., how to translate affine nested-loop programs with dynamic if-conditions into input-output equivalent PPNs in an automated way. The main research topic of this dissertation is how to translate dynamic programs with relaxation II and III into PPNs.

The first issue calls for a novel parallelization approach for dynamic programs. The second issue below addresses a novel approach for implementing a PPN.

• **Issue II**: we demonstrated that an exact communication model identification in PPNs derived from dynamic programs is not possible at compile-time. Therefore, we address the problem of communication model identification in PPNs derived from dynamic programs. This issue is an important optimization problem as it allows to identify communication models with simpler realization.

#### 1.4 Research Contributions

The work presented in this dissertation focuses on the derivation of Polyhedral Process Networks specifications from dynamic programs. Below, we list the contributions delivered by this dissertation.

- Contribution I [26, 27]: a first approach for automated translation of affine nested-loop programs with dynamic loop bounds (Dynloop) into input-output equivalent Polyhedral Process Networks. In addition, we present a method for analyzing the execution overhead introduced in the PPNs derived from programs with dynamic loop bounds.

- **Contribution II [28]:** a first approach for automated translation of affine nested-loop programs with *while*-loops (WLAP) into input-output equivalent Polyhedral Process Networks.

- **Contribution III [29]:** we present a formal procedure for communication models identification in Polyhedral Process Networks derived from the dynamic programs introduced in Section 1.2.

To address the first issue defined in Section 1.3, Contributions I and II of this dissertation devise a compile-time automated procedure that can be used to derive a PPN from dynamic programs with relaxations II and III presented in Section 1.2. By our third contribution we address the second issue: we introduce a novel procedure for Communication Model Identification in PPNs derived from dynamic programs.

#### 1.5 Related Work

The work presented in this dissertation is directly related to previous works on systematic and automated derivation of process networks from affine nested loops programs initiated by Rijpkema et al. [15, 30]. Further, Turjan et al. [31] proposed an automated derivation of process networks from *static* affine nested loop programs (SANLPs). In SANLPs the memory array subscripts, loop bounds and conditional control structures are affine constructs of surrounding loop iterators, program parameters and constants. Stefanov [21] further developed a procedure of process network derivation from more relaxed class of affine nested loop programs called *Weakly Dynamic Programs* (WDPs). In this class of affine nested loops programs, the conditions in control structures might be dependent on some information that is unknown at compile-time and may change at run-time. In contrast, this dissertation deals with more general class of applications, i.e., affine nested loop programs with loop bounds (Dynloop) that unknown at compile-rime and determined at run-time, and applications containing while-loops (WLAP).

In the context of automatic parallelization of sequential programs research has been done on approaches to convert a nested loop program to an equivalent program 1.5 Related Work 15

which is in a single-assignment form, i.e., a program in which every memory cell is written at most once. Such program is easier to be analyzed and parallelized efficiently. The work of Knobe and Sarkar [32], Feautrier et al. [33] and the work of Griebl, Lengauer and Collard [34–36] on this topic are directly related to the first step of our approaches presented in Chapters 3 and 4 of this dissertation. This is because in this step we propose an approach to convert dynamic programs into a single-assignment form which we call dynamic Single Assignment Code (dSAC). The relations are explained below.

Knobe and Sarkar [32] proposed an approach to convert a nested loop program to a single-assignment form that they call Array Static Single Assignment (ASSA). Their approach is more general than our approach in the sense that the class of nested loop programs which they can convert to their ASSA includes classes of dynamic programs considered in this dissertation which we can convert to our dSAC. However, when Dynloop and WLAP programs are considered, our approach is more efficient compared to their approach in the sense that dSAC is a more efficient single-assignment form in terms of code lines and memory usage compared to their ASSA form. This is because in our approach a dependence analysis is performed at compile-time before the corresponding dSAC is generated. This compile-time dependence analysis, called fuzzy array data-flow analysis (FADA) [37,38], allows an efficient code generation. The approach of Knobe and Sarkar does not perform any dependence analysis at compile-time. Instead, the dependence analysis is performed at run-time by placing a special code called  $\phi$  functions and @ arrays in their ASSA, thereby making their approach more general. The  $\phi$  functions and @ arrays introduce significant code overhead because in many cases unnecessary  $\phi$  functions and @ arrays are placed in the ASSA, thereby making the ASSA form very inefficient in terms of code lines and memory usage compared to our dSAC.

The work of Feautrier et al. in the context of the PAF parallelizer [39] describes an approach to convert nested loop programs similar to our dynamic programs into a single-assignment form called SA. Their approach is based on performing a fuzzy array data-flow analysis (FADA) at compile-time before generating the SA. The result of this FADA analysis is implemented by  $\phi$  functions placed in their SA during code generation. The  $\phi$  functions depend on parameters whose values have to be set dynamically at run-time in order to preserve the original data-flow when the control flow cannot be predicted at compile-time. The work of Feautrier et al. lacks a general approach to set the values of the parameters at run-time. The work described above relates to our approach for converting dynamic programs to a dSAC in the sense that we also perform a FADA analysis at compile-time and we also place a code with parameters in our dSAC similar to the  $\phi$  functions but our code is more efficient. Also, the difference is that we have developed a very simple general approach to set the values of the parameters at run-time. This approach is presented in Chapter 3.

Griebl, Lengauer and Collard [34–36] addressed the problem of parallelization of while-loops similar to our work. Similar to our approach, they perform array dataflow analysis to expose data dependencies in an explicit way. Subsequently, they use space-time restructuring techniques to generate the code for speculative execution

or software pipelining. Generally unscannable execution space that a while-loop provides, they scan with the help of run-time computable predicates, that are also used for detection of while-loops' termination. Besides introducing an overhead at run-time, these predicates limit the applicability of their approach to shared memory systems. In contrast, our parallelization approach targets multiprocessor systems with distributed memory.

Apart from the idea to convert a nested loop program to an equivalent program in a single-assignment form, in the context of automatic parallelization of dynamic sequential programs, there are a number of other efforts that were made.

Raman et al. [40] devise the Parallel-Stage Decoupled Software Pipelining (PS-DSWP) multi-threading technique to extract pipeline parallelism from codes with irregular, pointer-based memory accesses and arbitrary control flow, which generally include while-loops. A parallel-stage allows to obtain pipeline parallelism from some stages executed in a DOALL fashion. In contrast, our approach supports also task- and data-level parallelism besides the pipeline- and iteration-level parallelism. Moreover, we can generate parallel code for multi-processor systems with distributed memory.

The LooPo compiler [41] deals with parallelization of more general class of nested loop program than the class we consider in this dissertation. It includes nested loop programs with unscannable execution spaces which boundaries are determined at run-time. The proposed parallelization procedure is based on run-time detection of executed statements as well as detection of program termination [42]. In contrast to [41], we use FADA and perform approximated dependence analysis at compile-time. Moreover, we do as much as possible analysis at compile-time, thereby reducing the run-time overhead significantly.

A different approach is taken by Benabderrahmane et al. [43] where they embed the control and exit predicates to the general data-dependent control-flow programs. This predicates are used instead of data dependent control structures and while-loops as first-class citizens of the algebraic representation. Subsequently, a polyhedral representation is derived and code generation is performed from static program analysis. In this approach, hiding all dynamism (dynamic loop bounds, while-loops) in algebraic representations also diminishes the parallelism available in the initial program as less information is visible for analysis. By contrast, our technique exposes and utilizes all available parallelism.

Rauchwerger et al. [44] focused on parallelizing while-loops that are defined by one or more recurrences that can be detected at compile-time; a reminder that can be either analyzed statically or is unknown at compile-time; and one or more termination conditions. Although, they were able to parallelize a while-loop involving linked lists traversal, it is not shown how they would tackle more general while-loops, which we consider in this dissertation.

Bijlsma [45, 46] and Geuns [47] approach the problem of while-loops parallelization by considering an initial program with while-loops being in the local single assignment (LSA) form where all data dependencies are explicit. They implement the explicit data dependencies using circular buffers with overlapped read and write windows. Specifying a program in a LSA form can be very time consuming and error prone process because the system designer has to do the dependence analysis manually. We find this a very a limitation of their work. By contrast, our approach uses an automatic data-dependence analysis procedure which relieves the designer from the very difficult task to do the manual dependence analysis.

In the context of communication model identification in Process Networks, to the best of our knowledge, not much attention has been devoted to the problem of automatic communication model identification. An automatic procedure exists for communication model identification while translating *static* affine nested loop programs (SANLP) into functionally equivalent PPNs [31]. In this dissertation, we develop an extension to this procedure which identifies communication models in Polyhedral Process Networks derived from the dynamic programs introduced in Section 1.2.

#### 1.6 Dissertation Outline

The remaining part of this dissertation is organized a follows. In Chapter 2, we first introduce notations and terminology that will be used throughout the dissertation. Further, we present theory describing the Polyhedral Model and show how this model can be extracted from applications considered in this dissertation.

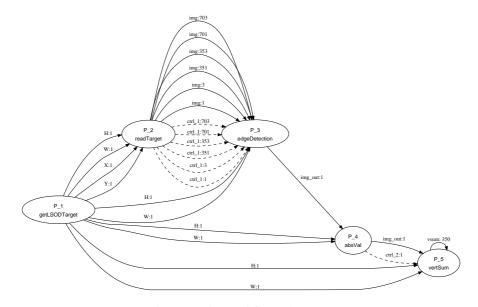

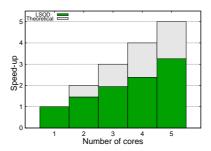

In Chapter 3, we present a first approach for automated translation of affine nested loop programs with dynamic loop bounds (Dynloop) into input-output equivalent Polyhedral Process Networks. The chapter describes in great details the models, methods, and techniques we have developed and used in the approach. First, we describe the techniques and procedures involved in the conversion of a Dynloop to our dynamic Single Assignment Code (dSAC). Second, we demonstrate how the free parameters introduced by FADA analysis are assigned in dSAC using control arrays. Third, we show how the topology of the corresponding PPN is derived, as well as the code executed in each process. Moreover, we demonstrate how the buffer sizes of FIFO channels are computed that guarantee a deadlock-free execution of a PPN.

In Chapter 4, we present a first approach for translation of *affine nested loop* programs with *while*-loops (WLAP) into input-output equivalent PPNs. In this chapter we describes in great details the models, methods, and techniques we have developed and used in the approach.

In Chapter 5, we present a formal procedure for identifying communication models in process networks derived from the dynamic programs introduced in Section 1.2. We formulate two problems from integer linear problems domain that allow us to identify the communication models presented in Section 1.1.2.

In Chapter 6, we present a case study that we conducted in order to validate and evaluate our approach presented in Chapter 3. This case study presents a real-life industrially relevant application. We will present a comprehensive analysis and re-

port the results we obtained in this case study.

Finally, we conclude this dissertation in Chapter 7 with a summary of the presented research work along with some concluding remarks.

# Background

In order to comprehend the next chapters, this chapter contains some basic material from the theory of integer linear algebra. Besides introduction of notations and definitions, this chapter deals with models of computation and compiler techniques used for parallelizing sequential programs.

Further, this chapter is organized as follows. Section 2.1 gives some notations and definitions used throughout the dissertation. We present the Polyhedral Model and show how this model can be extracted from SANLPs. Section 2.2 presents the formal definitions of the program models of dynamic applications introduced in Chapter 1. The parallelization approach presented in this dissertation deals with this type of dynamic programs only. Section 2.3 presents the definition of Polyhedral Process Networks model of computation which is used as a target parallel model of computation.

For better understanding of the solution approaches presented in the following Chapters, we give a brief overview of the two state-of-the-art techniques used to analyze sequential programs. The first one, called Exact Array Dataflow Analysis (EADA) [4], is used to analyze static programs, namely SANLPs. Recall, that EADA is implemented in the pn [48] compiler for the translation of SANLPs to PPN. We present EADA in Section 2.4.

The second technique, which we present in Section 2.5, allows for the analysis of programs with more relaxed constraints than SANLPs. That is, we consider the Fuzzy Array Dataflow Analysis (FADA) introduced in [37,38]. FADA is an enhanced version of EADA and it is used to analyze programs with dynamic behavior.

Finally, Section 2.6 briefly presents important definitions and theory used to identify communication models while deriving a Polyhedral Process Network specification.

#### 2.1 Preliminaries

The formal objects handled in this dissertation are mainly vectors with integer coordinates. A sub-vector of a vector  $\vec{x}$  built from components k to l is written as:  $\vec{x}[k..l]$ . Similarly,  $\vec{x}[i]$  is a shorthand for  $\vec{x}[i..i]$ . By  $\ll$  we denote lexicographical ordering of vectors. This is expressed as a set of equalities and inequalities as:

$$\vec{a} \ll \vec{b} \equiv \bigvee_{i=1}^{n} (\vec{a}[i] < \vec{b}[i] \land \bigwedge_{j=1}^{i-1} \vec{a}[j] = \vec{b}[j])$$

(2.1)

The smallest and the largest vectors according to  $\ll$  are the lexicographical minimum (lexmin) and lexicographical maximum (lexmax), respectively.

#### 2.1.1 Polyhedral Model

Sets of rational values described by affine inequalities have been the subject of extensive research and are called polyhedra.

#### Definition 2.1.1 (polyhedron)

The implicit definition of polyhedron is defined as the intersection of a finite set of closed linear half-spaces. Polyhedron is specified by a system of linear inequalities and equalities:

$$\mathcal{P}: \{\vec{x} \in \mathbb{Q}^n | A\vec{x} \ge \vec{b}\}$$

(2.2)

where A is a  $j \times n$  matrix,  $\vec{b}$  is a j-vector, and where n is the dimension of the space containing the polyhedron. The dimension of a polyhedron is defined to be the dimension of the smallest affine subspace which spans the polyhedron. A polyhedron of dimension d is called a d-polyhedron. Z-polyhedron [6] denotes a polyhedron whose points are integers.

#### Definition 2.1.2 (parameterized polyhedron)

The parameterized polyhedra is a family of polyhedra  $\mathcal{P}(\vec{p})$  described as a linear function of  $\vec{p}$ , which is an m-vector of parameters:

$$\mathcal{P}(\vec{p}) = \{ \vec{x} \in \mathbb{Q}^n | A\vec{x} + B\vec{p} \ge \vec{c} \}, \vec{p} \in \mathbb{Q}^m$$

(2.3)

where *A* and *B* are constant matrices and  $\vec{c}$  is a constant vector.

In the compilers domain, the input program is usually represented in some internal representation form. This form allows for manipulation and optimization, for example in the context of loop transformations. One of this special intermediate program formats called Polyhedral Model was originally introduced for systolic array synthesis but also was found useful for parallelizing compilers [4]. This model applies to the class of affine nested loop programs and is used in compiler optimizations to efficiently analyze and transform the input program.

2.1 Preliminaries 21

In the following, we demonstrate how the Polyhedral Model can be extracted from sequential programs considered in this dissertation.

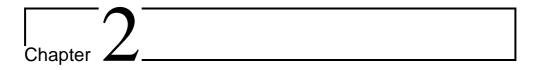

Figure 2.1: Geometrical representation of iteration domain of statement S2 in the program depicted in Figure 1.2(a).

The whole execution of a statement in a program can be described by the following constructs:

#### **Iteration domain**

The Iteration Domain (ID) is the set of values of an iteration vector for which a statement is executed. ID of a statement S is denoted by  $\mathbf{D}(S)$ . An *iteration vector*  $\vec{x}$  of a statement in a dynamic program is built from iterators of surrounding for- and while-loops. Although, an iterator for a *while*-loop may not be explicitly mentioned in the source code of a program, we can associate some "virtual" iterator  $w: 0 \le w$  with the *while*-loop.

Because the execution of a statement is guarded by an affine control, its iteration domain can be specified as a set of linear inequalities defining a Z-polyhedron. For example, consider statement S2 in Figure 1.2(a). Its iteration domain represented in algebraic form is the following parameterized polyhedron:

$$\begin{aligned} \mathbf{D}(\mathrm{S2}) &= \mathcal{P}(M,N) &= \\ &= \left\{ (i,j) \in \mathbf{Q}^2 \middle| \begin{array}{c} 1 & 0 \\ -1 & 0 \\ -1 & 1 \\ 0 & -1 \\ 0 & -1 \end{array} \right] \begin{pmatrix} i \\ j \end{pmatrix} \geq \begin{bmatrix} 1 \\ -N \\ 0 \\ -M \\ -2 \end{bmatrix}, \begin{bmatrix} 1 & 0 \\ -1 & 0 \\ 0 & 1 \\ 0 & -1 \end{bmatrix} \begin{pmatrix} M \\ N \end{pmatrix} \geq \begin{bmatrix} 1 \\ -10 \\ 1 \\ -10 \end{bmatrix} \right\} = \\ &= \left\{ (i,j) \in \mathbf{Q}^2 \middle| 1 \leq i \leq N \land i \leq j \leq M \land j \leq 2 \land 1 \leq M \leq 10 \land 1 \leq N \leq 10 \right\}. \end{aligned}$$

For illustrative purposes, the ID of statement S2 in a graphical form is shown in Figure 2.1. Similarly, the iteration domain in algebraic form of statement S2 shown

in Figure 1.5(c) is:

$$\mathbf{D}(S2) = \{(i, w) \in \mathbb{Q}^2 \mid 1 \le i \le N \land 0 \le w \land 1 \le N \le 10\}.$$

#### Order of execution

In an affine nested loop programs statements evaluate some data. An evaluation of a single statement W on iteration point  $\vec{x}$  is called an *operation* and is denoted as  $\langle W, \vec{x} \rangle$ , where  $\vec{x} \in \mathbf{D}(W)$ .

The schedule determines the execution order of all operations of all statements in a program. The execution order of operations can be established using the sequencing predicate  $\prec$ . An operation  $\langle W, \vec{x} \rangle$  is evaluated before an operation  $\langle R, \vec{y} \rangle$  ( $\langle W, \vec{x} \rangle \prec \langle R, \vec{y} \rangle$ ) according to the program sequence if: 1) iteration point  $\vec{x}$  lexicographically precedes iteration point  $\vec{y}$ ; or 2) if  $\vec{x} = \vec{y}$  and statement W precedes statement R in the program code. The sequencing predicate depends only on the code of a sequential program. Let  $N_{WR}$  be the number of loops enclosing both statement W and W. Let v0 be the textual order of statements W1 and W2 in the code of the program. Then the execution order is given by:

$$\langle W, \vec{x} \rangle \prec \langle R, \vec{y} \rangle \equiv \vec{x}[1..N_{WR}] \ll \vec{y}[1..N_{WR}] \lor (\vec{x}[1..N_{WR}] = \vec{y}[1..N_{WR}] \land W \lhd R) \tag{2.4}$$

[4] shows how sequencing predicate  $\prec$  can be expanded to a system of linear inequalities.

## 2.2 The Program Model

In the following, we will give definitions of the type of sequential programs we consider in this dissertation.

#### Definition 2.2.1 (static affine nested loop program, SANLP)

A **static affine nested loop program (SANLP)** is a program where each program statement is enclosed by one or more for-loops and if-statements, and where:

- 1. loops have a constant step size;

- 2. loops have bounds that are affine expressions of the enclosing loop iterators, static program parameters, and constants;

- 3. if-statements have affine conditions in terms of the loop iterators, static program parameters, and constants;

- 4. index expressions of array references are affine functions of the enclosing loop iterators, static program parameters, and constants;

- 5. data flow between statements is explicit via a variable or an array.

An example of a SANLP is given in Figure 1.2(a).

#### Definition 2.2.2 (Weakly Dynamic Program, WDP)

A **Weakly Dynamic Program (WDP)** is a program where each program statement is enclosed by one or more for-loops and if-statements, and where:

- 1. loops have a constant step size;

- 2. loops have bounds that are affine expressions of the enclosing loop iterators, static program parameters, and constants;

- 3. **if-statements have no restrictions on conditions** the condition of *if* can be an arbitrary function of program variables, enclosing loop iterators, static program parameters, and constants;

- 4. index expressions of array references are affine functions of the enclosing loop iterators, static program parameters, and constants;

- 5. data flow between statements is explicit via a variable or an array.

An example of a WDP program is given in Figure 1.5(a).

Definition 2.2.3 (affine nested loop program with dynamic loop bounds, Dynloop) An affine nested loop program with dynamic loop bounds (Dynloop) is a program where each program statement is enclosed by one or more for-loops and if-statements, and where:

- 1. loops have a constant step size;

- 2. **loops have no restrictions on the bounds** the bounds of for-loops can be an arbitrary expression of program variables, the enclosing loop iterators, static program parameters, and constants;

- 3. **if-statements have no restrictions on conditions** the condition of **if** can be an arbitrary function of program variables, enclosing loop iterators, static program parameters, and constants;

- 4. index expressions of array references are affine functions of the enclosing loop iterators, static program parameters, and constants;

- 5. data flow between statements is explicit via a variable or an array.

An example of a Dynloop program is given in Figure 1.5(b).

#### Definition 2.2.4 (affine nested loop program with while-loops, WLAP)

An **affine nested loop program with while-loops (WLAP)** is a program where each program statement is enclosed by one or more for-loops, **while-loops** and **if**-statements, and where:

- 1. for-loops have a constant step size;

- 2. loops have no restrictions on the bounds the bounds of for-loops can be an arbitrary expression of program variables, the enclosing loop iterators, static program parameters, and constants;

- 3. if-statements have no restrictions on conditions the condition of *if* can be an arbitrary function of program variables, enclosing loop iterators, static program parameters, and constants;

- 4. index expressions of array references are affine functions of the enclosing loop iterators, static program parameters, and constants;

- 5. data flow between statements is explicit via a variable or an array.

An example of a WLAP program is given in Figure 1.5(c).

### 2.3 Polyhedral Process Networks

Below, we give a definition of the Polyhedral Process Network Model of Computation.

#### Definition 2.3.1 (Polyhedral Process Network, PPN)

The PPN model of computation is a special case of the Kahn Process Networks (KPN) [7] model of computation with the following properties:

- it consists of concurrent autonomous processes;

- processes communicate data in a point-to-point fashion over bounded FIFO channels via ports;

- processes synchronize via blocking read/write on an empty/full FIFO;

- processes have a well defined structure consisting of read, execute and write code sections;

- it is deterministic:

- it has a distributed control.

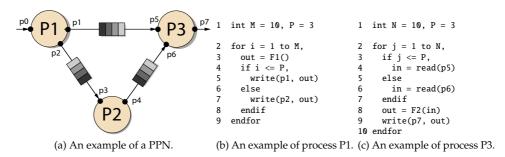

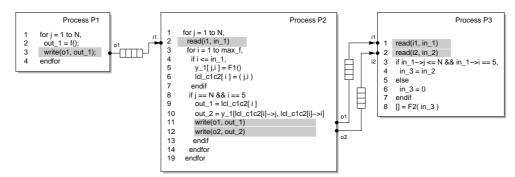

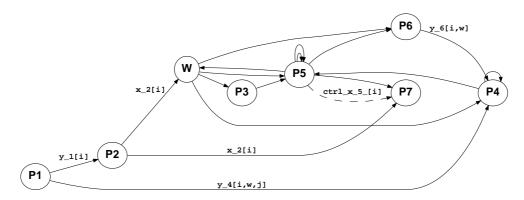

An example of a PPN is illustrated in Figure 2.2(a). The PPN consists of three processes, P1, P2 and P3, and three FIFO channels. The examples of code of processes P1 and P3 of this PPN are illustrated in Figure 2.2(b) and Figure 2.2(c), respectively. In order to see the well defined structure of every process on a PPN, consider the source code of process P3 in Figure 2.2(c). In the *read* section at lines 3–7, the process reads data from two ports p5 or p6. In the *execute* section at line 8, the process executes function F3() on data that has been read. In the *write* section at line 9, the process

Figure 2.2: An example of a PPN and source codes of its processes P1 and P3.

writes the produced data to port p7. This clearly separated structure of a process in a PPN allows for explicit separation between computation and communication.

In a PPN, every process can be described by the following terms.

#### Definition 2.3.2 (node domain)

A Node Domain (ND) of process P executing function F in a PPN is the set of iteration points  $ND_{P_F}$  for which function F is executed.

In this dissertation we consider PPNs where every process executes only one function, and, therefore, for the sake of brevity, we can use  $ND_{P_F} = ND_P$ . A node domain of a process can be represented by a polyhedron. In Section 2.1.1, it has been demonstrated that a set of iteration points can be represented as a Z-polyhedron. Similarly, a node domain of a process can be represented as a Z-polyhedron. For example, consider process P1 of PPN shown in Figure 2.2(a). The code of process P1 is illustrated in Figure 2.2(b). The process executes function F1(), and, thus, its node domain is  $\mathbf{D}(ND_{P1}) = \{i \in \mathbb{Z} | 1 \leq i \leq M \land M = 10\}$ .

#### Definition 2.3.3 (input port domain)

An input port domain (IPD) of port p is the set of iteration points  $I_p \in IPD_p$  for which port p is read.

#### **Definition 2.3.4 (output port domain)**

An output port domain (OPD) of port q is the set of iteration points  $O_q \in OPD_q$  for which port q is written.

Similarly to a node domain, IPDs and OPDs of every process can be represented as Z-polyhedra. For example, consider source codes of processes P1 and P3 depicted in Figure 2.2(b) and Figure 2.2(c), respectively. Processes are connected via output port p2 (see line 7 in Figure 2.2(b)) of process P1 and input port p5 (see line 4 in Figure 2.2(c)) of process P3. Therefore, input and output port domains of ports p5 and p2 are  $\mathbf{D}(IPD_{p5}) = \{j \in \mathbb{Z} | 1 \leq j \leq N \land j \leq P \land N = 10 \land P = 3\}$ , and  $\mathbf{D}(OPD_{p2}) = \{i \in \mathbb{Z} | 1 \leq i \leq M \land i > P \land M = 10 \land P = 3\}$ .

A FIFO in a PPN is connected to processes which writes and reads via ports. For every FIFO, there exists a mapping function that maps the iteration points of IPD of the process that reads from the FIFO to the iteration points of OPD of the process that writes to the FIFO. Consider a FIFO connected to processes via ports p and q.

#### **Definition 2.3.5 (mapping function)**

A mapping function is an affine mapping  $f_{pq}: I_p \to O_q: O_q = f(I_p)$ , where  $I_p \in IPD_p$  and  $O_q \in OPD_q$ .

An example of the mapping function between ports  $p_1$  and  $p_5$  of processes P1 and P3 in the PPN shown in Figure 2.2(a) is  $f_{p_5p_1}: \mathbb{Z} \to \mathbb{Z}: j = i*1, i \in IPD_{p_5}, j \in OPD_{p_1}$ .

#### 2.4 Exact Array Dataflow Analysis

Because our approach of parallelizing dynamic programs presented in the following chapters is an extension of the parallelization approach of static programs, for better understanding, in this section we formally describe the EADA [4] algorithm, which is used to perform dependence analysis on static programs only. We will demonstrate an application of the EADA algorithm on the static program depicted in Figure 1.2(a).

The goal of the dependence analysis is to determine if evaluation of a statement depends on evaluation of other statements and to find these evaluations. For example, in the SANLP program depicted in Figure 1.2(a), the purpose of the dependence analysis is to find whether statement *S*3 depends on statements *S*1 or *S*2 via array y and at which iterations. Or in other words, for every element of array y read at a given iteration of statement *S*3, the dependence analysis finds which statement, *S*1 or *S*2, and at which iteration it writes data to the given array element. The result of the analysis forms the dependency relations between iterations of statements writing/reading to/from the array.

Consider two statements W and R, and operations  $\langle W, \vec{x} \rangle$  and  $\langle R, \vec{y} \rangle$ , where the first operation writes to an array and the second operation reads from it. The operation  $\langle W, \vec{x} \rangle$  is a source for operation  $\langle R, \vec{y} \rangle$  if it satisfies the system of linear (in)equalities (2.5). Note, that all iteration vectors of operations that satisfy this system form a convex domain.

$$\mathbf{Q}_{WR}(\vec{y}) = \{ \vec{x} \mid \vec{x} \in \mathbf{D}(W), \qquad (c1)$$

$$\mathcal{I}_{W}(\vec{x}) = \mathcal{I}_{R}(\vec{y}), \qquad (c2)$$

$$\langle W, \vec{x} \rangle \prec \langle R, \vec{y} \rangle \}. \qquad (c3)$$

(2.5)

The first constraint (c1) states that the source iteration  $\vec{x}$  has to exist, i.e., it has to belong to the iteration domain of statement W. The constraint (c2) specifies that if

there is a dependency between two operations, both have to access the same array element. To access an array element, operation  $\langle W, \vec{x} \rangle$  uses an affine indexing function  $\mathcal{I}_W()$  and operation  $\langle R, \vec{y} \rangle$  uses an affine indexing function  $\mathcal{I}_R()$ . The (c3) constraint determines an order of operations, i.e., source operation  $\langle W, \vec{x} \rangle$  has to be evaluated before operation  $\langle R, \vec{y} \rangle$ .

There might be many operations of a single statement satisfying system (2.5), i.e., writing to the same array element. However, only the "last" writing operation is the source for operation  $\langle R, \vec{y} \rangle$ . Therefore, the source operation is the lexicographical maximum between all operations satisfying system  $\mathbf{Q}_{WR}(\vec{y})$ :

$$\mathbf{K}_{WR}(\vec{y}) = lexmax\{\mathbf{Q}_{WR}(\vec{y})\}. \tag{2.6}$$

So far, operations of only single statement have been considered, while there might be several statements  $W_1, ..., W_m$  writing to the same array element. In this case, all pairs  $W_1/R, ..., W_m/R$  have to be considered. The actual source is the "last" operation between all operations of all statements:

$$\sigma(\langle R, \vec{y} \rangle) = lexmax\{\langle W_k, \mathbf{K}_{W_k R}(\vec{y}) \rangle \mid k \in [1, m]\}. \tag{2.7}$$

For example, consider the program in Figure 1.2(a). There are two statements, S1 and S2 writing to array y and one statement S3 reading from that array. Therefore, we consider two pairs S1S3 and S2S3. For each pair we build the system of linear inequalities (2.5) as depicted in Table 2.1 (see  $\mathbf{Q}_{S1S3}((i_3, j_3))$  and  $\mathbf{Q}_{S2S3}((i_3, j_3))$ ). With  $(i_3, j_3)$ , we denote the iteration vector (i, j) of statement S3.

| $\overline{\mathbf{Q}_{\mathrm{S1S3}}((i_3,j_3))}$ | $\mathbf{Q}_{\mathrm{S2S3}}((i_3,j_3))$                               |      |

|----------------------------------------------------|-----------------------------------------------------------------------|------|

| $1 \le k \le M$                                    | $1 \le i_2 \le N \land i_2 \le j_2 \le M \land $ $j_2 \le 2$          | (c1) |

| $k = j_3$                                          | $j_2 = j_3$                                                           | (c2) |

| true                                               | $\langle S2, (i_2, j_2) \rangle \prec \langle S3, (i_3, j_3) \rangle$ | (c3) |

Table 2.1: Examples of system (2.5) for S1S3 and S2S3 statements.

Finding lexicographical maximums,  $\mathbf{K}_{S1S3}()$  and  $\mathbf{K}_{S2S3}()$ , of the systems in Table 2.1 means to solve the Parametric Integer Linear Problems (PILPs) depicted in Table 2.2. The solution to find the maximum point for a given convex domain is based on the dual simplex method [16] that is implemented in open-source libraries such as *isl* [17], Parma Polyhedral Library [18], and PIPLib [19].

The source operation  $\sigma(\langle S3, () \rangle)$  is found by determining the *lexmax* between  $\mathbf{K}_{S1S3}()$  and  $\mathbf{K}_{S2S3}()$  which is another PILP problem. Finally, the source operation  $\sigma(\langle S3, (i_3, j_3) \rangle)$  for the data read by statement S3 can be written in the following form:

Objective:

$$lexmax\{(i_3, j_3)\}\ lexmax\{(i_3, j_3)\}\$$

subject to:  $Q_{S1S3}((i_3, j_3))$   $Q_{S2S3}((i_3, j_3))$

Table 2.2: PILP problems for pairs S1S3 and S2S3.

$$\sigma(\langle S3, (i_3, j_3) \rangle) = \begin{vmatrix} \mathbf{if} & j_3 \leq 2 \\ \mathbf{then} & \langle S2, (i_3, j_3) \rangle \\ \mathbf{else} & \langle S1, (j_3) \rangle. \end{vmatrix}$$

(2.8)

Both branches of the if-statement in Solution (2.8) shown above represent solutions of the PILP problems formulated in Table 2.2. The if-condition is derived by finding the lexicographical maximum by Equation 2.7. Solution (2.8) can be interpreted as follows: the source of the data for statement S3 of the program in Figure 1.2(a) can be two statements – the source is statement S1 when the iterator j of S3 is greater than 2, otherwise, the source is statement S2.

## 2.5 Fuzzy Array Dataflow Analysis