# Transformations for Polyhedral Process Networks

Sjoerd Meijer

## Transformations for Polyhedral Process Networks

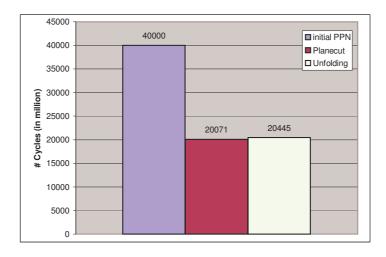

#### **Proefschrift**

ter verkrijging van

de graad van Doctor aan de Universiteit Leiden,

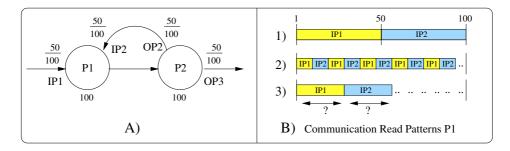

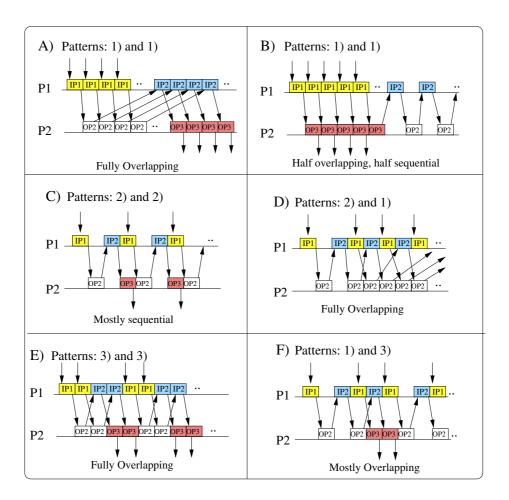

op gezag van Rector Magnificus prof.mr. P.F. van der Heijden,

volgens besluit van het College voor Promoties

te verdedigen op woensdag 8 december 2010

klokke 16:15 uur

door

Sjoerd Meijer

geboren te Leiderdorp

in 1979.

#### Samenstelling promotiecommissie:

promotor Prof.dr. Ed F. Deprettere Universiteit Leiden co-promotor Dr. Todor Stefanov Universiteit Leiden

overige leden: Prof.dr. Harry Wijshoff Universiteit Leiden

Prof.dr. Joost Kok Universiteit Leiden

Prof. Dr.-Ing. Jürgen Teich Universität Erlangen-Nürnberg

Prof.dr. Gerard Smit Universiteit Twente

Prof.dr. Henk Corporaal Technische Universiteit Eindhoven

Transformations for Polyhedral Process Networks

Sjoerd Meijer. Thesis Universiteit Leiden. - With index, ref. - With summary in Dutch

ISBN 978-90-9025792-1

Copyright ©2010 by Sjoerd Meijer, Leiden, The Netherlands. Cover design by Senny Yu.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in the Netherlands

# Contents

| 1 | Intr              | roduction                                                                                                                                | 1                                                  |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 1.1               | Problem Statement                                                                                                                        | 5                                                  |

|   | 1.2               | Contributions                                                                                                                            | 7                                                  |

|   | 1.3               | Related Work                                                                                                                             | 9                                                  |

|   | 1.4               | Outline                                                                                                                                  | 15                                                 |

| 2 | Bacl              | kground                                                                                                                                  | 17                                                 |

|   | 2.1               | Polyhedra                                                                                                                                | 17                                                 |

|   | 2.2               | Lexicographic Order                                                                                                                      | 19                                                 |

|   | 2.3               | Static Affine Nested-Loop Programs                                                                                                       | 21                                                 |

|   | 2.4               | Extracting the Polyhedral Model from SANLPs                                                                                              | 23                                                 |

|   | 2.5               | Polyhedral Process Networks                                                                                                              | 24                                                 |

|   | 2.6               | Validity of Transformations                                                                                                              | 29                                                 |

|   |                   |                                                                                                                                          |                                                    |

| 3 | Proc              | cess Splitting Transformations                                                                                                           | 31                                                 |

| 3 | <b>Proo</b> 3.1   | cess Splitting Transformations  Process Splitting: Definitions, Notations, and Examples                                                  | <b>31</b> 32                                       |

| 3 |                   | • •                                                                                                                                      | -                                                  |

| 3 | 3.1               | Process Splitting: Definitions, Notations, and Examples                                                                                  | 32                                                 |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples                                                                                  | 32<br>35                                           |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation Partitioning Metrics | 32<br>35<br>38                                     |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation Partitioning Metrics | 32<br>35<br>38<br>38                               |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation Partitioning Metrics | 32<br>35<br>38<br>38<br>39                         |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation Partitioning Metrics | 32<br>35<br>38<br>38<br>39<br>40                   |

| 3 | 3.1<br>3.2        | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation                      | 32<br>35<br>38<br>38<br>39<br>40<br>42             |

| 3 | 3.1<br>3.2<br>3.3 | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation                      | 32<br>35<br>38<br>38<br>39<br>40<br>42<br>42       |

| 3 | 3.1<br>3.2<br>3.3 | Process Splitting: Definitions, Notations, and Examples Challenges of Applying the Process Splitting Transformation                      | 32<br>35<br>38<br>38<br>39<br>40<br>42<br>42<br>43 |

| viii | Contents |

|------|----------|

|      |          |

|   |     | 3.5.3 Four Producers with Delays                                 | 59  |

|---|-----|------------------------------------------------------------------|-----|

|   | 3.6 | Discussion and Summary                                           | 62  |

| 4 | Pro | cess Merging Transformations                                     | 65  |

|   | 4.1 | Process Merging: Definitions                                     | 65  |

|   | 4.2 | Challenges of Applying the Process Merging Transformation        | 66  |

|   | 4.3 | Restrictions on the Throughput Modeling                          | 69  |

|   | 4.4 | Throughput Modeling                                              | 70  |

|   |     | 4.4.1 Process Throughput and Throughput Propagation              | 70  |

|   |     | 4.4.2 Isolated Throughput of a (Compound) Process                | 72  |

|   |     | 4.4.3 FIFO Channel Throughput                                    | 74  |

|   |     | 4.4.4 Aggregated FIFO Throughput                                 | 75  |

|   |     | 4.4.5 System Throughput Calculation Algorithm                    | 77  |

|   | 4.5 | Case-Studies                                                     | 78  |

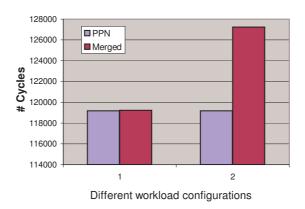

|   |     | 4.5.1 Merging Light-Weight Producers                             | 78  |

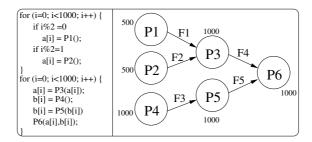

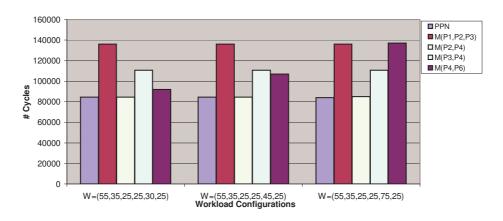

|   |     | 4.5.2 Merging Processes in Networks with Different Data Paths .  | 81  |

|   | 4.6 | Discussion and Summary                                           | 82  |

| 5 | App | ling Transformations in Combination                              | 85  |

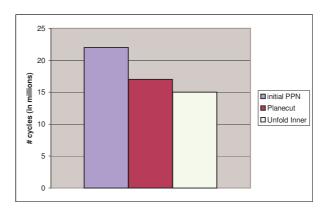

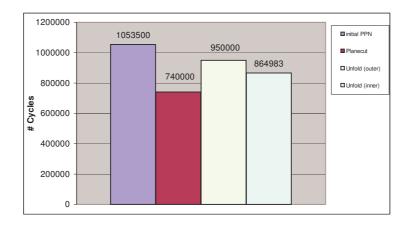

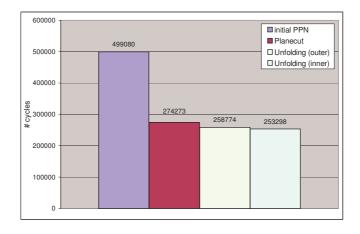

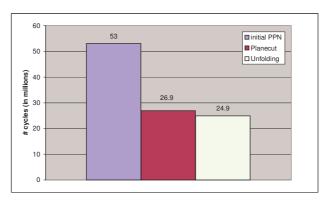

|   | 5.1 | Impact of the Transformation on Performance Results              | 87  |

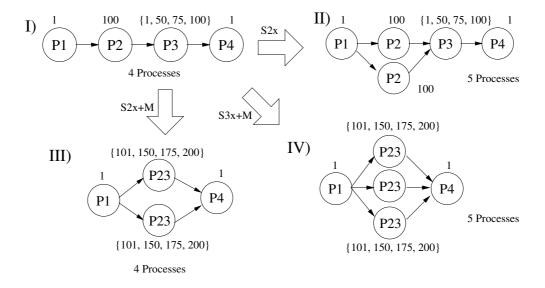

|   |     | 5.1.1 Transforming a PPN to Create More Processes                | 87  |

|   |     | 5.1.2 Transforming a PPN to Reduce the Number of Processes       | 89  |

|   |     | 5.1.3 The Optimization Pitfall: Performance Degradation          | 90  |

|   | 5.2 | Compile-Time Solution for Transformation Ordering                | 91  |

|   |     | 5.2.1 Creating Load-Balanced Tasks                               | 93  |

|   |     | 5.2.2 Selecting Processes for Transformations                    | 94  |

|   | 5.3 | Exploiting Data-Level Parallelism                                | 95  |

|   |     | 5.3.1 Stateful Processes                                         | 97  |

|   |     | 5.3.2 Cycles                                                     | 97  |

|   | 5.4 | Case-Studies                                                     | 99  |

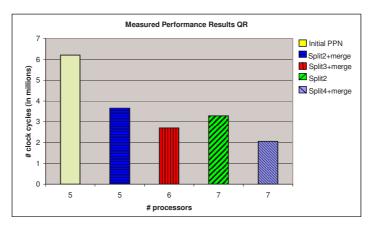

|   |     | 5.4.1 QR Decomposition: a PPN with Stateful Processes and Cycles | 100 |

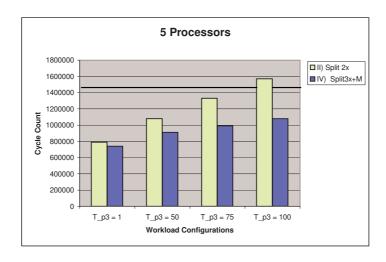

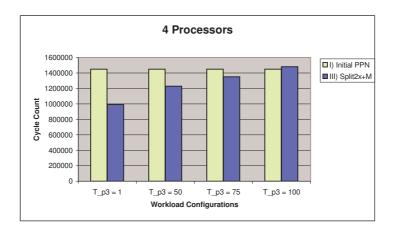

|   |     | 5.4.2 Transforming Perfectly Balanced PPNs                       | 102 |

|   | 5.5 | Discussion and Summary                                           | 105 |

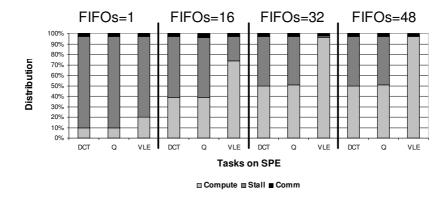

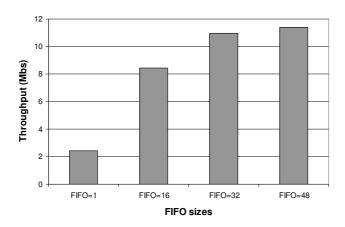

| 6 | Exe | cuting PPNs on Fixed Programmable MPSoC Platforms                | 111 |

|   | 6.1 | The Programmable Platforms                                       | 112 |

|   | 6.2 | Realizing FIFO Communication                                     | 114 |

|   | 6.3 | Performance Results                                              | 118 |

|   | 6.4 | Discussion and Summary                                           | 123 |

| 7 | Con | clusions                                                         | 125 |

| Contents         | ix  |

|------------------|-----|

| Bibliography     | 130 |

| Index            | 140 |

| Acknowledgments  | 143 |

| Samenvatting     | 145 |

| Curriculum Vitae | 147 |

|         | 4 |  |  |  |

|---------|---|--|--|--|

| 1       |   |  |  |  |

|         |   |  |  |  |

| 1       |   |  |  |  |

| I       |   |  |  |  |

| Chanter |   |  |  |  |

| Chapter |   |  |  |  |

In 1965, Moore predicted that the number of transistors on a semiconductor and thus the overall chip performance would double every two years [56]. This has become known as Moore's law and due to the minitiurization of transistors, chip manufactures were able to produce faster, more powerful processors every year. Moore's law has proven to be correct for many years, but it was also clear that this trend had to come to an end at some point in time. Moore also stated that "no physical quantity can continue to change exponentially forever". Today, chip manufactures have to deal with electrical power leakage and heat dissipation as a result of packing more and more transistors into a smaller area. In addition, the minitiurization of transistors has reached its physical limits and it cannot further help in producing faster processors.

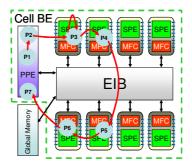

As a solution to produce more powerful processors, multi/many-core processor architectures were introduced. Multi/many-core processors consist of multiple processors, possibly of the same type, and are interconnected and integrated into a single chip. Hence, the name Multi-Processor Systems on-Chip (MPSoC). For example, mainstream consumer PCs nowadays come with dual/quad core processors, game consoles such as the PlayStation 3 and its Cell processor have 9 cores [39], GPUs have 128 stream processors, and cell phones have many different compute and hardware components. Inspired by Moore's law, many people believe that the new trend is an exponential growth of the number of cores in processors. Processors, however, are only a small part of complex systems that are shipped to the market. Equally important is the entire software-stack that provides services to end-users and developers. A powerful processor is useless without good compilers, debuggers, simulators, operating systems, libraries, etc. So the programmability of a processor highly determines its success.

If we consider software compilers for single processors with a sequential execution model, then it is widely accepted that they do a reasonably good job in auto-

matically translating high-level program descriptions into low-level machine code. When the compiler technology for single processors matured, it raised the programming abstraction level and gave a boost to the productivity of developers and greatly improved maintainability and portability of program code. Both the hardware and compilers focused on exploiting Instruction Level Parallelism (ILP) as much as possible. Single processor architectures support ILP with superscalar, out-of-order, and instruction pipelining techniques implemented in hardware. For other architectures, such as VLIW [26] and EPIC [73] processors, it is the compiler's responsibility to find parallel instructions. Therefore, much research has been done in techniques such as automatic vectorization, software pipelining, and other scheduling techniques to overlap instructions (ILP) as much as possible.

While the programming of a single processor is already a difficult task, there is now another dimension of complexity with the introduction of Multi-Processor System on Chips (MPSoCs). The programming of these multi-processor systems is a difficult and time consuming process as it involves careful partitioning and assignment of program tasks to different processing elements of the MPSoC platform. A program task can for example be a function, i.e., a set of instructions, that reads function input arguments, performs some computations, and write the results to its function output arguments. Overlapping different program tasks by executing them in parallel at different processors of the MPSoC platform can result in significantly reduced execution times. This illustrates that besides Instruction Level Parallelism (ILP), that Task Level Parallelism (TLP) is an important factor that needs to be taken into account in programming MPSoC platforms. Exploiting TLP is difficult as the different program tasks need to synchronized and must also exchange data in a particular way, which makes the programming of MPSoC platforms more difficult than a single processor system. So the question is: how can MPSoC platforms be efficiently programmed using the available resources of the hardware platform?

If we roughly classify the different approaches to program Multi-Processor System on Chips (MPSoCs), we see that it is either the programmer's responsibility to create different program tasks, or a compiler oriented approach where program tasks are automatically extracted from sequential program specifications. Examples of the former approach are new programming languages (e.g., OpenCL [64], StreamIT [87]), language extensions (e.g., CUDA [59]), compiler pragma's (e.g., OpenMP), and libraries (e.g., Pthreads, MPI [27]). Examples of the latter are parallelizing compilers that extract program tasks or threads from sequential code (e.g., the Intel compiler [10], Pluto [13], SUIF [36], Polaris [12]). Parallelizing compilers is the subject of the work presented in this dissertation. The Leiden Embedded Research Center (LERC) has developed a tool-flow to program embedded Multi-Processor Systems on Chip (MPSoC) in a systematic and automated way. To be more specific, the goal is to make the programming more easy and to present a solution for the question raised

earlier: how to efficiently program an MPSoC. The LERC's solution relies on two basic principles: i) a parallel Model of Computation (MoC) must be used to specify an application, and ii) this parallel specification should be executed on a hardware platform that exactly matches the MoC.

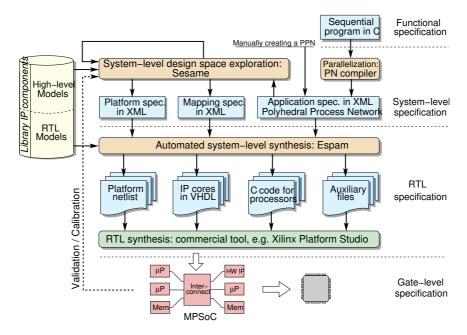

Figure 1.1: Daedalus tool-flow overview

The Daedalus tool-flow [61] that is being developed by LERC and shown in Figure 1.1, aims at providing a complete solution for system-level design of MPSoC platforms. It implements the two principles described above. From this tool-flow, let us consider first the functional specification of the application that a designer should provide. The first part of LERC's solution to make the programming of MPSoCs easier, relies on the fact that application developers find it more easy to specify an application as a sequential program as opposed to writing a parallel one. At the same time, we know that a parallel application specification can be mapped onto a parallel architecture more naturally than a sequential program. So, the idea is to combine the best of these worlds by deriving an equivalent parallel specification from sequential program specifications. This has resulted in the open-source pn compiler [95], that is part of the Daedalus tool-flow as shown in Figure 1.1. The pn compiler translates applications specified as Static Affine Nested-Loop Programs (SANLP), i.e., a subset of the C language as we discuss in Chapter 2, to Polyhedral Process Networks (PPNs) [8]. The PPN Model of Computation consists of autonomously running pro-

cesses with private memory and control that communicate over point-to-point FIFO channels using blocking FIFO read/write primitives (discussed in detail in Chapter 2).

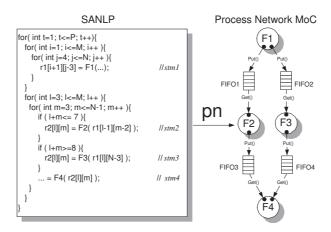

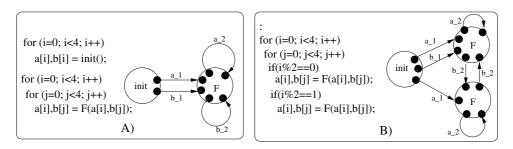

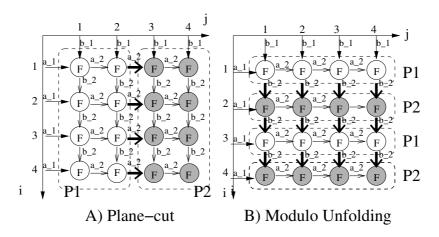

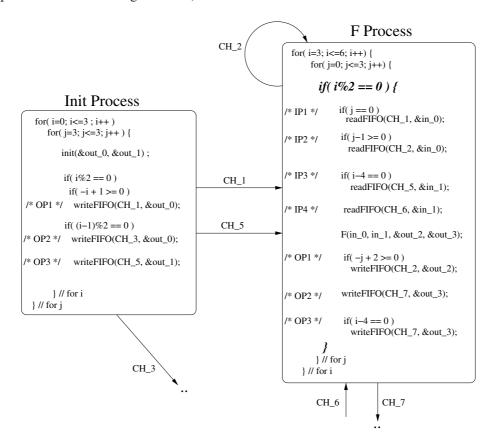

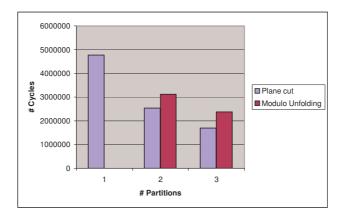

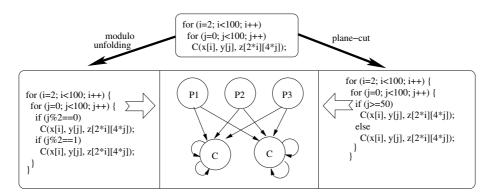

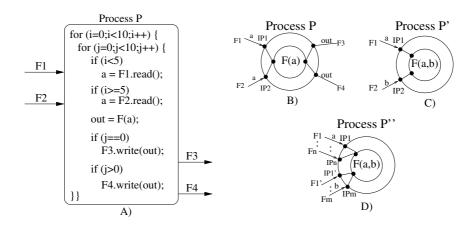

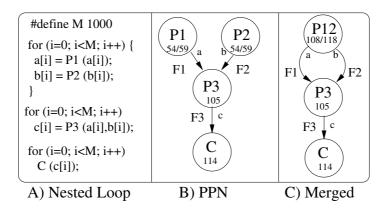

Figure 1.2: Compiling a Static Affine Nested-Loop Program (SANLP) to a Polyhedral Process Network

The derivation of a PPN from a static affine nested-loop programs is illustrated with an example in Figure 1.2. This example is taken from [89] and reveals how program statements are translated to processes and how array accesses are replaced by FIFO read/write statements. In Figure 1.2, a sequential program with 4 program statements is shown at the left-hand side. The statement's variable indexing functions are affine expressions in the loop iterators and static program parameters. The derived and functionally equivalent PPN for this code is shown at the right-hand side. Each program statement is translated to a process, and the array accesses have been replaced with read and write functions such that the processes only communicate data over FIFO channels.

Let us now consider the second design step of the Daedalus tool-flow, i.e., the translation from the system-level specification of the MPSoC platform to the RTL specification of the platform, as shown in Figure 1.1. The idea of the Daedalus tool-flow, is to generate a hardware platform that "natively" supports the execution of Polyhedral Process Networks (PPNs). That is, the ESPAM platform executes PPNs very efficiently because the operational semantics of the process network model of computation are supported with hardware components. For example, data communication and process synchronization of processes are realized by distributed memories, which can be organized as one or more FIFOs. Thus, blocking FIFO read/write primitives are hardware supported and make the processes to be self-scheduled very efficiently. Furthermore, the ESPAM platform allows processes to be assigned to independent

Instruction Set Architecture (ISA) components and/or IP-cores that must exist in the library of predefined IP components. The ESPAM tool automatically generates a hardware platform prototyped on an FPGA board based on 3 specifications as shown at the system specification level in Figure 1.1. The first specification is a high-level platform specification describing only the number of processing elements and the inter-connect of the platform. The second is an application specification in the form of a PPN that can be generated by the pn compiler, but can also be specified by hand. The third is a mapping specification describing how the processes of the PPN are assigned to the processing elements of the hardware platform. The ESPAM tool takes these 3 specifications as an input, and creates the corresponding RTL specification of the MPSoC platform and maps the PPN process threads onto IP-cores and/or programmable processors. Thus, we see that the Daedalus tool-flow enables designers to implement a sequential program specification onto a multi-processor system on chip in a systematic and automated way.

#### 1.1 Problem Statement

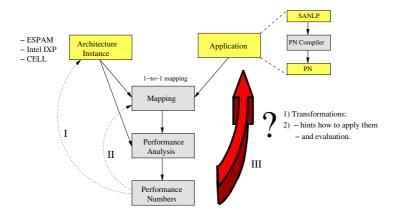

The Y-chart approach is a very general iterative system-level design methodology [44]. Figure 1.3 illustrates this approach and captures the iterative process of getting

Figure 1.3: The Y-chart Approach

to a satisfactory design point. It takes an application specification and a platform specification. Then, after executing the application onto the platform, performance numbers are obtained for a particular design point. The performance of an application can be measured by considering the execution time or throughput of that application on a simulator or the real hardware platform. If the design point does not meet the

performance or resource constraints (i.e., the constraints on the number of tasks assigned to a processing element), then the platform, application and/or mapping can be adjusted accordingly. By iteratively changing some parameter values in this design methodology, the implementation should converge to, for example, the desired performance. Let us now project the different aspects of the Y-chart approach onto the Daedalus tool-flow. Recall that the Daedalus tool-flow (see Figure 1.1) takes the application, platform, and mapping specifications as an input, as shown in the Y-chart approach, and allows a designer to create and program an MPSoC platform. In addition, the Sesame tool [67, 88] that is integrated into Daedalus, can be used for design-space exploration at the system-level of abstraction. The Sesame tool, however, only explores different platform and mapping instances. These two designspace exploration aspects correspond to arrows I and II in the Y-chart approach, see Figure 1.3. The Daedalus tool-flow does *not* support the third exploration aspect, i.e., the exploration of different application instances as indicated with the bold arrow III in the Y-chart. Although some transformations have been defined to change a PPN application specification [79], i.e., to reduce/increase the number of processes in a PPN, the Daedalus tool-flow does not give any hints or tips to the designer how to apply these transformations in order to transform a PPN in the best possible way. Applying transformations as part of the tool-flow is the subject of this dissertation. It is crucial to assist the designer in applying the transformations in the best possible way since there are many possibilities to transform an application to meet the performance requirements or resource constraints. In this dissertation, we do not investigate different mapping strategies and always assume to have a 1-to-1 mapping of processes to processors. Thus, the grouping or splitting of tasks is not achieved by different mapping strategies, but by the pn compiler instead, i.e., we focus on the pn compiler that is used to derive PPNs from sequential program specifications. Although the pn compiler relieves the designer from the difficult and error-prone task of identifying and synchronizing different program partitions, it is not guaranteed that the performance/resource constraints are met. Recall that the pn compiler uses a partitioning strategy that creates a single thread for each program statement in the sequential code. As one program statement can be much more computationally intensive than others, the corresponding process network may be highly imbalanced not meeting the performance and resource constraints. Therefore, we formulate the first problem area as follows.

• Issue I: It is unlikely that all the designer's constraints are met in one translation step of the Daedalus tool-flow. That is, the Daedalus tool-flow can quickly generate a single design point, and can also explore different architecture and mapping instances by means of simulation. It, however, does not provide any compile-time infrastructure and hints/heuristics to transform and evaluate dif-

1.2 Contributions 7

ferent application instances. Transforming application instances is crucial to meet the performance/resource constraints. Moreover, the compile-time hints are not only necessary to assist the designer in making the correct design decisions, but also to reduce the number of design points a designer should consider/evaluate. Therefore, the main research topic of this dissertation is to assist the designer in transforming a PPN specification to obtain a satisfactory design point as illustrated with the bold arrow III in Figure 1.3.

The first issue as discussed above addresses the program specification in the design process. A second addresses the target platform specification. The Daedalus tool-flow targets FPGA based platforms and creates an instance of the ESPAM execution platform. That is, an execution platform prototyped on an FPGA that matches the process network model of computation. However, such a specific platform may not always be available to a designer and we therefore formulate a second issue.

• Issue II: Currently, the Daedalus tool-flow aims at creating an MPSoC instance that exactly matches the process network model of computation on an FPGA based platform, but such a specific platform may not always be available. We want to investigate how to execute polyhedral process networks on programmable, off-the-shelf multi-processor platforms. This means that the different components of the process network model of computation must be mapped onto fixed hardware components of the target platform.

#### 1.2 Contributions

To address the first issue as defined in Section 1.1, we define compile-time approaches to transform and thus optimize PPNs. These optimizations consist of compile-time guided application of transformations that restructure PPNs in a certain way. First, we briefly review the transformations as they have been defined in [78,79] and then we present the contributions.

The first transformation is a process splitting transformation which increases the number of processes in a PPN, and the second is the process merging transformation which reduces the number of processes in a polyhedral process network:

- 1. The *process splitting* transformation is a transformation that copies program statements, comparable to the classical loop-unrolling transformation. As a result, the derived process network has multiple processes executing the same function possibly in parallel.

- 2. The *process merging* transformation achieves the opposite of the splitting transformation and groups, clusters, or merges several processes into one compound

process. The functions in the merged processes will be executed sequentially in the compound process.

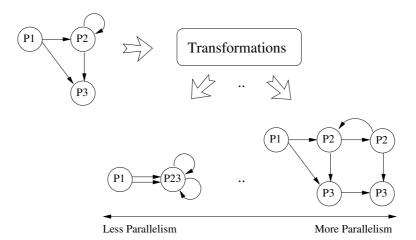

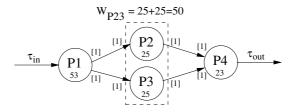

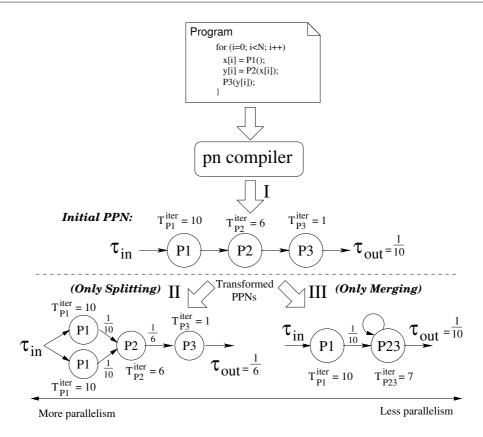

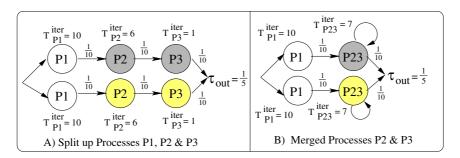

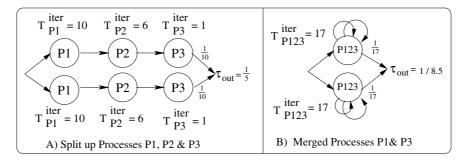

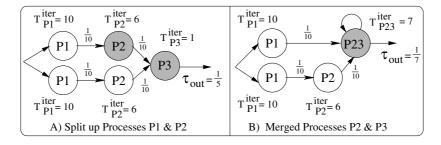

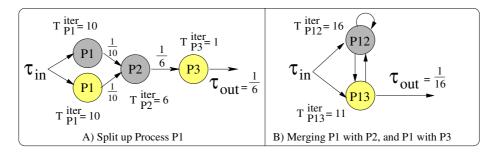

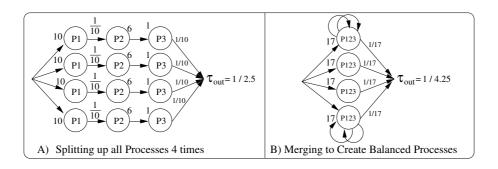

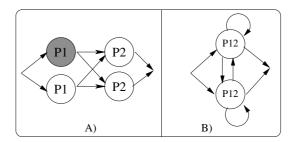

Using these two transformations, an initial process network can be optimized to meet performance/resource constraints. The arbitrary PPN example shown in Figure 1.4, consists initially of 3 processes. Using the process merging transformation, processes P2 and P3 can be sequentialized into compound process P23. Thus, we say that less parallelism is exploited. By using the process splitting transformation, processes P2 and P3 can be split up to create extra copies. As a result, more processes can execute in parallel and thus we say that more parallelism is exploited.

Figure 1.4: Deriving Different PPNs using Process Splitting and Merging Transformations

- Contribution I [51, 53]: our first contribution consists of compile-time solution approaches for process splitting and merging to assist the designer in achieving his performance/resource requirements:

- The process splitting transformation: a process can be split up in many different ways and many factors influence the final performance results.

We identify factors and define corresponding metrics that play a key role in the performance results, and show an analytical approach to calculate and evaluate them at compile-time. The analysis is performed locally on the process that is selected for splitting [51].

- The process merging transformation: we define a throughput model for Polyhedral Process Networks (PPN). This allows the designer to evaluate

1.3 Related Work 9

the throughput of different transformed networks derived from the same PPN. The designer, thus, can select the merging alternative with the best throughput. The throughput model is used for a global analysis of the entire network, as opposed to the splitting transformation, since the effects of the merging cannot be studied only by locally looking into the processes to be merged [53].

- Contribution II [52]: we present a holistic approach to use both the process splitting and process merging transformation in combination. This is a necessity to obtain good performance results that cannot be achieved by using only one transformation. Our solution approach solves the problem of ordering the different transformations and the problem of identifying the most suitable processes to merge/split. We create a number of load-balanced compound processes equal to the number of tasks a designer wants to create that can, for example, be the available processing elements of the target platform. In the holistic approach, we use the results of *Contribution I* to decide how the processes can be best split up, and the throughput model can be used for evaluating the solutions.

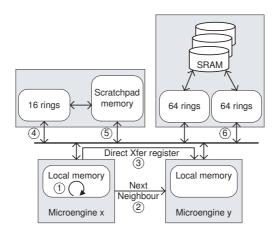

- Contribution III [50,58]: to address the second issue presented in Section 1.1, i.e., the programming of standard and off-the-shelf MPSoC platforms, we present approaches to execute PPNs onto the Intel IXP Network Processor and the Cell Processor. Thus, we investigate how to efficiently realize FIFO communication using the provided communication infrastructures of these platforms.

#### 1.3 Related Work

The research work presented in this dissertation contributes to the underlying theory of the Daedalus tool-flow [61], and hence it contributes to the the research area of tool-flows for systematic and automated application-to-platform mapping, which has been widely studied in the research community. As it is an extensive research area, we first give a brief overview of related tool-flows. Then, we describe in more detail the related work with respect to the specific contributions of this dissertation.

To start with the frameworks, the System-On-Chip Environment (SCE) [21] enables designers to go from a specification all the way down to a hardware/software implementation. The Program State Machine (PSM) is used as a model of computation, which brings together concepts of hierarchical concurrent finite-state machines, dataflow graphs and imperative programming languages in a single model of computation [28, 33]. Basically, it encapsulates basic algorithms written in C, providing the designer in this way with the flexibility to manually write C and to manually parti-

tion the code in a particular way using a data flow model. This is different from the Daedalus approach, as the designer only writes the sequential top-level application description. It is the responsibility of the pn compiler to partition the code and to derive a polyhedral process network. The functionality of the processes in the Daedalus tool-flow can be specified by the designer as sequential functions in C, similar to SCE, or as IP-cores from the component library.

A second related framework is SystemCoDesigner, which maps applications specified in SystemC onto a heterogeneous platform [42]. Similar to the SCE approach, it is the designer's responsibility to write an actor orientated application in SystemC, whereas the Daedalus tool-flow derives Polyhedral Process Networks (PPNs) from a sequential program. Similar to Daedalus, it allows to create a heterogeneous MPSoC by instantiating and connecting cores from a component library. In addition, actors in SystemCoDesigner can be implemented as a hardware accelerator using the Forte Cynthesizer. The high-level synthesis of processes to hardware is currently not (yet) supported by Daedalus. A research work in the context of the Daedalus tool-flow explored the VHDL synthesis of processes in a PPN using PICO [91], but it is not integrated into the Daedalus tool-flow and thus not available yet.

Two more frameworks that provide a complete environment for modeling applications, design space exploration, prototyping and synthesis of MPSoC platforms are Koski [41] and PeaCE [35]. The main difference between Daedalus and Koski is that the functionality of the system in Koski is described with an application model in an UML environment. And PeaCE, that is short for Ptolemy extension as a Codesign Environment, restricts itself to SDF graphs and finite state machines as the model of computation.

Next, we briefly discuss four frameworks that focus more on the software part of MPSoC platforms. MAPS is a framework for MPSoC application parallelization [15]. It provides a set of tools which guides the parallelization processes. In contrast to our analytical compile-time parallelization approach, MAPS parallelization is mainly based on profile information and manually written Kahn Process Network (KPN) specifications. It provides a source-to-source translation, i.e., the output code is threaded C code that can be compiled with other compilers to the target platform. MAMPS [45] is another tool-flow that maps SDF graphs onto MPSoC platforms. Besides the difference that they map SDFs, the work focuses on homogeneous MPSoCs consisting of MicroBlaze processors that are point-to-point connected. Daedalus supports heterogeneous platforms and interconnects such as crossbars and shared busses. On the other hand, MAMPS supports the mapping of multiple applications, while Daedalus currently supports only single application mapping. The Distributed Operation Layer (DOL) [84] is another framework for specifying and mapping parallel applications onto heterogeneous multiprocessor platforms. The target platform is a

1.3 Related Work 11

fixed tiled multi-processor embedded system. As an application model, Kahn Process Networks (KPNs) are used that are specified manually by the designer. In the performance analysis, a technique is used based on real-time calculus, which has some similarities with our throughput model used to evaluate process merging transformation, i.e., the second contribution of this dissertation. We discuss this in more detail when we discuss the related work for the process merging transformation. In the design space exploration of DOL, mainly different mappings are evaluated, but different instances of the KPN application are not explored. As a last framework, we briefly discuss Metropolis [5]. It uses a pre-defined platform such that the system design problem is reduced to mapping the desired functions onto the given platform. Metropolis is a very general framework as it does not define any specific design tools, such as for example Daedalus. Instead, based on a meta-model with formal semantics, it allows designers to simulate, formally analyze, and synthesize complex systems.

Next, we discuss the related work with respect to the specific contributions of this dissertation, i.e., the process network transformations and the mapping of PPNs onto programmable MPSoCs.

Our process splitting transformation is related to the loop unrolling transformation used in compiler design [57]. The relation is that both transformations aim at enhancing parallelism in a sequential program. However, loop unrolling enhances instruction level parallelism by copying a loop body several times and re-indexing the variables in the body, thus creating more parallel instructions and reducing the loop control overhead. In contrast, our splitting transformation enhances task-level parallelism by copying a program statement a number of times such that these copies can be encapsulated in concurrent processes. In [77], splitting and re-timing transformations are described for improving block schedules for Homogeneous Synchronous Data Flow (HSDF) graphs by exploiting inter-iteration parallelism. This is related to our splitting transformation in the sense that the latter also facilitate the exploitation of inter-iteration parallelism available in a SANLP when such program is converted to a set of PPN specifications. In [66], Parhi and Messerschmitt describe a splitting transformation developed to be applied on iterative data-flow programs. This transformation is similar to our splitting in that both transformations increase the number of tasks in a program and exploit the hidden concurrency for static programs. The main difference between our work and the work presented in [66, 77] however, is that we have devised an approach to evaluate the quality achieved by applying the transformations when targeting a particular MPSoC platform. We show in this dissertation, that there are several factors that must be taken into account when deciding what transformation to apply in order to improve the system performance. In contrast, in [77] the transformations are applied on the HSDF graph corresponding to an application where no information about the target implementation platform is con-

sidered. In [83], Teich and Thiele propose an approach to partition affine dependence algorithms for mapping onto reduced/fixed size processor arrays. Their approach is based on two transformations called Expand and Reduce. This relates to our work in the sense that process splitting transformations are also an approach to partition algorithms. However, there are two important differences. First, the result of the partitioning, i.e., the generated PPNs are suitable for mapping onto heterogeneous multi-processor platforms. Second, by using our process splitting transformations we do a reverse partitioning compared to the approach of Teich and Thiele. They start with a dependence graph (DG) representation of an algorithm which is the partitioning of an algorithm. Then they apply tiling (grouping) on the DG representation to obtain a desired partitioning in which less parallelism is exploited. In contrast, we start with a SANLP, derive a PPN, and by applying process splitting we partition the computational workload onto several processes. That is, in the proposed approach we take into account the characteristics of a particular MPSoC target platform and evaluate the quality of different (possible) transformations, thereby obtaining a desired partitioning in which more parallelism is exploited.

When we look at the **process merging** transformation, then we see that many related research works focus on the merging of tasks or processes, which is called clustering in the domain of Synchronous Data Flow (SDF) graphs [47]. These works, however, mainly deal with the code generation of clustered or grouped tasks itself [9, 23]. We analyze and model networks with a given compound process and schedule to compare different PPN instances by defining and using a throughput model, see Chapter 4. There are other works on throughput computation, but they are developed for SDF and CSDF models [30,55], which are less expressive models than the PPN model we use. Besides the difference in the models of computation, there is also a difference in the analysis. That is, in [30] two approaches are presented to calculate the throughput of SDFGs based on either the conversion of SDF to Homogeneous SDF or on state space exploration. In both cases, the disadvantage is that the number of actor or states, respectively, can explode. The advantage, however, is that cyclic graphs can also be analyzed, while our approach is restricted to acyclic process networks. Another work also investigated the trade-offs in buffer requirements and throughput constraints for SDFs [80], and in a follow up also for cyclo-static dataflow graphs [81]. The analysis, again, relies on state-space exploration techniques, but it does investigate buffer requirements that we omitted in our throughput model. The reason is that we assume buffer sizes that give maximum performance, which are calculated by the pn compiler. Another main difference with these works is that we use the throughput model for evaluating and comparing the process splitting and merging transformations, while the throughput models for (C)SDF graphs focus only on buffer sizes and throughput. Thus, they do not investigate any transformations. Another analytical model for analyzing embedded real-time systems is network calculus [46] and an ex1.3 Related Work 13

tension of this which is called real-time calculus [16, 85]. The analysis is based on the minimum and maximum number of events that arrive in a time interval, which are called the arrival curves. In a similar way, service curves are defined, which represent upper and lower bounds of the available resources in an interval. Based on given traces of event streams, timing properties, on-chip memory requirements, and the load on different platform components can be analyzed. This is different from our approach as we only analyze the throughput of the process network given the workload of each process. Thus, our approach does not require to have the event stream of the system, which may be difficult to obtain. In the network calculus, however, the minimum and maximum arrival of events are propagated and thus also the dynamic behavior is captured. In our approach, we calculate an average throughput and thus the dynamic throughput behavior of processes is not captured. It makes, however, our throughput model simple and very efficient to compare different network instances and process merging transformations. As a consequence, however, our approach does not analyze the memory requirements/constraints. While the network calculus does analyze the memory requirements, it can suffer from some inaccuracies when the bounds on the event streams are not tight. Finally, an approach is presented in [22] to automatically synthesize a multiprocessor architecture for process networks under particular mapping and performance constraints. This is different from our work as the process networks are not analyzed and transformed.

The second contribution of this dissertation deals with a holistic approach to combine process splitting and merging transformations, which is most closely related to the work in [31] that aims at exploiting coarse-grained task, data and pipeline parallelism in stream programs. The StreamIt [87] compiler derives stream graphs which are mapped on the Raw architecture and has optimizations for filter fusion and fission [32], comparable to our process merging and splitting transformations. In their approach, they start to fuse filters until a certain point and then perform fission on this coarsed-grain task to create more data-level parallelism. The fusion is performed as long as the result of each fusion is stateless. We show in Chapter 5 that processes with state (self-edges) and networks with cycles can also be fissed and that performance gains are possible, which is not considered in [31]. A second difference is that we derive process networks from sequential programs written in C and not in a language, such as the StreamIt language, that has constructs to specify filters and FIFO communication and each kernel has a single input and single output channel. The processes in our polyhedral process networks can have multiple input/output channels and can read/write all or a subset of these channels. In [14], another approach is shown for mapping stream programs onto heterogeneous multiprocessor systems. A partitioning algorithm is presented that takes as input a graph, and outputs a mapping to fuse kernels to tasks. In an iterative manner, tasks are merged, kernels are moved from bottleneck processors, and tasks are created. Similar to the StreamIt approach, an

annotated version of the C programming language is used, and only stateless kernels are split for greater parallelism. Besides the average load of each kernel on each processor, similar to the workload of our processes, an additional parameter is required to be obtained from run-time analysis. That is, the average date rate on each stream that must be obtained from a profile.

In [68], the scheduling of Synchronous DataFlow (SDF) graphs [47] to parallel targets focused on partitioning and scheduling techniques that exploit task and pipeline parallelism. To schedule a SDF graph, a precedence graph is first constructed, which exposes the available data level parallelism. Then, to limit the explosion of nodes, clustering is applied and thus composite nodes are created. A fundamental difference with our work is that workloads are not taken into account in the clustering as we discuss in Chapter 5. And in addition to this, polyhedral process networks are more expressive than SDFs as FIFO channels can be read/written in a way that are described by (parameterized) polytopes. Thus, FIFO reads/writes can occur in some patterns, similar to the cyclo-static dataflow graphs (CSDF) [11], with the difference that the cycles in PPNs can be very large as they are derived from nested-loop programs. The R-Stream compiler [54] is a proprietary high level compiler for stream programs. It also uses the polyhedral model to partition code and data for a parametric parallel machine. The work focuses on the re-scheduling of computations (e.g., modulo scheduling) and placing explicit communications (e.g., DMA calls) to automatically put a multi-buffering scheme in place. Thus, the focus is on scheduling at the level of statement instances, and not on tasks/processes that can contain many statement instances as in our case.

The third contribution of this dissertation investigates the mapping of polyhedral process networks onto programmable MPSoC platforms such as the Intel IXP network processor and the Cell processor. We have developed source-to-source translation tool-flows to generate compilable source-code for the different components of PPNs. i.e, the processes and FIFO channels as we discuss in Chapter 6. To program the IXP, some high-level programming models have been developed. This basically means that the developer can use some higher-level languages and abstractions, e.g., the possibility to compose a number of operations that work on streams of data, and that assembly language is not a developer's only option. NP-Click [75] is one example as it offers an abstraction of the underlying hardware. Another effort for improving the programming of an IXP, is the  $\mu$ L programming language and the  $\mu$ C compiler by Network Speed Technologies [29, 82]. The difference with our approach is that both NP-Click and  $\mu$ L programming language, obviously, focus very much on internet packet handling, while we are interested in a programming model that supports the class of stream-based applications. Intel on the other hand, has developed an auto-partitioning C compiler as described in [49], which is therefore more closely related to our approach. An input application is specified as a set of 1.4 Outline 15

sequential C programs, which are called packet processing stages (PPSes). These PPSes closely correspond to the Communicating Sequential Processes (CSP) model of computation [37]. However, to express a program in PPSes is the responsibility of a programmer. In contrast, the pn compiler automatically generates PPNs from applications written as static affine nested loop programs [95].

Regarding the Cell processor, a great number of research works have been published since its introduction: ranging from case-studies and application specific implementations, to frameworks that deal with parallelization and mapping of applications onto the Cell. One model-based project that is similar to our approach in programming the Cell BE platform is the architecture-independent stream-oriented language StreamIt, which shares some properties with the Synchronous DataFlow (SDF) model of computation. The Multicore Streaming Layer (MSL) [99] framework realizes the StreamIt language on the Cell BE platform thereby focussing on automatic management and optimization of communication between cores. All data transfers are explicitly controlled by a static scheduler. This is different from our approach, since we use the PPN model of computation where the processes synchronize and communicate data over FIFO channels using blocking read/write primitives in absence of a global scheduler. A PPN is therefore self-scheduled, which can have as an advantage that there is no central scheduler that can become the bottleneck of the system. On the other hand, the blocking FIFO communication is software implemented, which makes it expensive communication primitives to use. As a last difference, and already discussed in this section, the SDF MoC used by StreamIt is less expressive Model of Computation (MoC) than our PPN MoC. Besides frameworks that support the parallel execution of applications, there are also communication libraries that focus more on the low-level communication infrastructure of the Cell, such as for example the Cell Messaging Layer [65]. It presents a similar idea as in our approach, i.e., a receiver initiated communication scheme as we will discuss in Section 6.1. However, the library offers just low-level send and receive primitives without focusing on the realization of more complex communication schemes such as FIFO reads/writes.

#### 1.4 Outline

The remaining part of this dissertation is organized as follows.

In Chapter 2, we first introduce the basic terminology and show with a simple running example how polyhedral process networks are derived from sequential static affine nested-loop programs.

In Chapter 3, we present the first process network transformation, i.e., the process splitting transformation. We define the metrics that play an important role in process

splitting and give a solution approach how these can be evaluated at compile-time to select the best partitioning.

In Chapter 4, we discuss the second transformation, i.e., the process merging transformation. In order to evaluate which merging is the best, we define a throughput model for process networks such that the throughput for a given PPN can be calculated and evaluated.

In Chapter 5, we present a holistic approach to transform PPNs using the process splitting and merging transformations in combination. We show that it is necessary to use both transformations to achieve the best performance results that cannot be achieved using one transformation only.

In Chapter 6, we present approaches to realize FIFO communication for executing polyhedral process networks on the Intel IXP network and the Cell BE processors. Both platforms are instances of programmable MPSoCs platform, but each with their own characteristics. While the IXP has hardware support for FIFO communication to some extent, the CELL must implement FIFO communication completely in software.

Finally, we conclude this dissertation in Chapter 7 with a summary of the presented research work along with some concluding remarks.

In this chapter, we give the definitions and notations that are used throughout the rest of this dissertation, i.e., we review some basic mathematical notations and definitions as discussed in for example [72, 74]. We thereby focus on polyhedra and the polyhedral model that are used by compiler optimizations to efficiently analyze and transform input programs. Then, we define the input programs, i.e., the class of applications, that can be analyzed with this polyhedral model and show an example of a Polyhedral Process Network (PPN). We discuss the structure and properties of PPNs, which is necessary to understand the chapters that deal with analyzing and transforming PPNs.

## 2.1 Polyhedra

The scalar product or inner product of two vectors  $\mathbf{a}$  and  $\mathbf{b}$ , denoted by  $\mathbf{a} \cdot \mathbf{b}$ , is defined as  $\mathbf{a} \cdot \mathbf{b} = \mathbf{a}^T \mathbf{b} = \sum_{i=1}^n a_i b_i$ , where  $a = (a_1, ..., a_n)$  and  $b = (b_1, ..., b_n)$  are column vectors. Note that  $\mathbf{a} \cdot \mathbf{b} = \mathbf{0}$  iff vectors  $\mathbf{a}$  and  $\mathbf{b}$  are orthogonal or  $\mathbf{a} = \mathbf{b} = 0$ .

Given a non-zero vector  $\mathbf{y}$  in  $\mathbb{R}^n$  and a constant  $\alpha$ , the following sets of points are defined:

- A hyperplane  $H = \{ \mathbf{x} \mid \mathbf{x} \cdot \mathbf{y} = \alpha \}.$

- A closed half-space  $H = \{ \mathbf{x} \mid \mathbf{x} \cdot \mathbf{y} \ge \alpha \}$ .

- An open half-space  $H = \{ \mathbf{x} \mid \mathbf{x} \cdot \mathbf{y} > \alpha \}$ .

An affine hyperplane is a (d-1)-dimensional hyperplane in a d-dimensional space, and thus divides the space in exactly two parts. A line, for example, is an affine

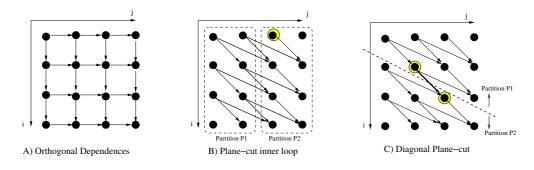

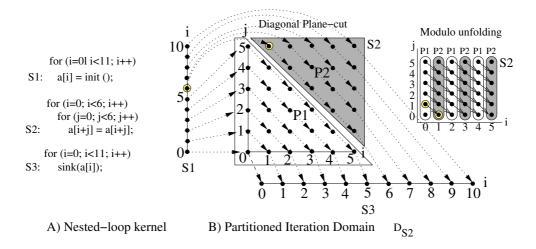

hyperplane in a 2-dimensional space, but not in a 3-dimensional space. We will use hyperplanes to define a polyhedron, but also in the process splitting transformation to partition processes in PPNs (see Chapter 3).

A **rational polyhedron**  $\mathcal{P}$  is a subset of  $\mathbb{Q}^d$  bounded by a finite number of closed half-spaces, i.e.,

$$\mathcal{P} = \{ \mathbf{x} \in \mathbb{Q}^d \mid A\mathbf{x} \ge \mathbf{b} \} \tag{2.1}$$

where A is an integral  $m \times d$  matrix, and b is an integral vector of size m.

A **polytope** is a bounded polyhedron.

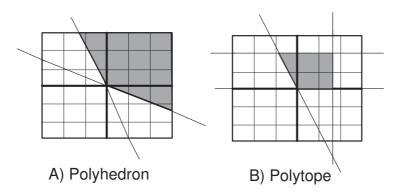

Figure 2.1 shows two 2-dimensional spaces with a number of closed half-spaces defining two polyhedra. The purpose of this example is to show the difference between a polyhedron and polytope. In Figure 2.1 A), a polyhedron is shown that is defined by only two constraints. As a result, the polyhedron is unbounded because there are no constraints on the maximum values that the points can have. In contrast, Figure 2.1 B) shows 4 lines/constraints that encapsulate all points within the grey area, which makes it an example of a bounded polyhedron, i.e. a polytope.

Figure 2.1: Polyhedron vs. Polytope

Polyhedra can also depend on a vector of parameters, denoted by  $\mathbf{p}$ , and we therefore define a parameterized polyhedron, denoted by  $\mathcal{P}(\mathbf{p})$ .

A parameterized polyhedron  $\mathcal{P}(\mathbf{p})$  is a polyhedron whose closed half-spaces are affinely dependent on a vector of parameters  $\mathbf{p} \in \mathbb{Q}^d$ , i.e.,

$$\mathcal{P}(\mathbf{p}) = \{ \mathbf{x} \in \mathbb{Q}^d \mid A\mathbf{x} \ge B\mathbf{p} + \mathbf{b} \}$$

(2.2)

where A is an integral  $m \times d$  matrix, B is an integral  $m \times n$  matrix, and b is an integral vector of size m.

We use polyhedra to model all iterations of a program statement in nested-loop programs. That is, we extract and use the polyhedral model to efficiently analyze and transform input programs, which we further discuss in Sections 2.4 and 2.5. In Section 2.2, we first discuss how different points in a set can be compared and ranked using Parametric Integer Linear Programming (PILP) techniques.

### 2.2 Lexicographic Order

In program analysis, many problems can be formulated as a Parametric Integer Linear Programming (PILP) problem. An example of such a problem is to find the first, or last, array element accessed by a program statement in a nested-loop. Thus, parametric integer programming [24], [74] is used to find exact solutions and feasible points ranked according to a lexicographic order. In program analysis of nested-loop programs, we are dealing with sets of integer vectors defined by linear inequalities. If we consider a set S as an example, then recall from Section 2.1 that it is defined as  $S = \{x \in \mathbb{Z}^d \mid Ax \geq b\}$  with  $A \in \mathbb{Z}^{m \times d}$  and  $b \in \mathbb{Z}^d$ . Then, parametric integer linear programming is used to find the minimum or maximum point in set S. And two points  $a \in \mathbb{Z}^n$  and  $b \in \mathbb{Z}^n$  in set S can be compared by using the lexicographic order.

We say that **a** is **lexicographically smaller** than **b**, denoted by  $\mathbf{a} \prec \mathbf{b}$ , if for the first position i in which both vectors are different, we have a(i) < b(i). This is expressed as a set of equalities and inequalities as:

$$\mathbf{a} \prec \mathbf{b} \equiv \bigvee_{i=1}^{n} (a(i) < b(i) \land \bigwedge_{j=1}^{i-1} a(j) = b(j))$$

(2.3)

Let us take as an example a set S with 5 elements:  $S = \{(1,1), (1,2), (2,1), (2,2), (2,3)\}$ . Using Formula 2.3, we see that (1,1) is lexicographical smaller than (1,2), denoted by  $(1,1) \prec (1,2)$ , because  $(1=1 \land 1 < 2)$ . Similarly, we see that (1,1) is lexicographical smaller than (2,3), i.e.,  $(1,1) \prec (2,3)$ , because comparing the first component of both points gives (1<2). Element (1,1) is the smallest element of set S and we define it as the lexicographical minimum element, denoted by lexmin. Similarly, we also define the lexicographical maximum point as the largest element, denoted by lexmax. For set S, element (2,3) is the largest element. The problem of finding the lexicographical minimum/maximum point within a set of linear constraints can be solved with PILP. The example set S as we have defined it above

can also be represented by a set of constraints, i.e.,  $S = \{(i,j) \in \mathbb{Z}^2 \mid 1 \leq i \leq 2 \land 1 \leq j \leq 3\}$ , and the ILP problem (no parameters are used in this example) can be subsequently formulated as shown in Table 2.1.

| Objective:  | $lexmin\{(i,j)\}$ |

|-------------|-------------------|

| Subject to: | $1 \le i \le 2$   |

|             | $1 \le j \le 3$   |

Table 2.1: Constraint system

The solution to find the minimum point for a given convex domain is based on the dual simplex algorithm [48] that is implemented in open-source libraries such as isl [93], Parma Polyhedral Library [4], and Piplib [24]. On a very high-level, the idea of the PIP algorithm and dual simplex method, is to find a minimum real point for a given convex set. Then, iteratively, new constraints are added not removing any integer points from the set. These libraries will thus find (1,1) as the lexicographical minimum, and (2,3) as the lexicographical maximum point.

Using the lexicographical order, it is also possible to rank an iteration point in polyhedra.

**Definition 1** The rank of a point  $p \in \mathcal{P}$ , is a number  $n \in \mathbb{Z}$  denoting all points that are lexicographical smaller than p.

For example, let us consider point (i = 1, j = 3) of the filter function call statement in Figure 2.3 B). To rank this point, we use the lexigraphical order to determine all points that precede (1,3). Therefore, we first consider all points that are smaller in the first component of point (1,3), i.e., i < 1. The points that satisfy this constraint, corresponds to all points within the top most and largest grey box in Figure 2.3 B); for all these points i = 0. In addition, we consider the points that have the same value in the first component, but which have a smaller value in the second component, i.e.,  $i = 1 \land j < 3$ . This corresponds to all points within the second and smallest grey box in Figure 2.3 B). Thus, the rank of point (1,3), corresponds to the number of elements in the set  $(i < 1 \lor (i = 1 \land i < 3))$ , i.e., all greyed points in Figure 2.3 B). If we assume N = 100, then the rank of (1,3) is 100+2 = 102, which is thus obtained by counting the number of points in a set. Counting the number of points in (parametric) polyhedra, i.e., the enumeration of (parametric) polyhedra, is a research field in itself. The basic idea is to derive a quasi-polynomial that describes the number of integer points in a polytope  $\mathcal{P}$ . For an in-depth discussion, the reader is referred to, for example, the works [18], [97]. In this dissertation, we use that work which is implemented in the polyhedral library PolyLib [98]. Thus, when we want to know the cardinality, or the number of points, of a set S, which we denote by |S|, then we use the counting functions from these libraries.

## 2.3 Static Affine Nested-Loop Programs

In Section 2.5, we consider parallel application specifications that are functionally equivalent to sequential program specifications that are static affine nested-loop programs. These are the subject of this section.

**Definition 2** A static affine nested loop program (SANLP) is a program where each program statements is enclosed by one or more loops and if-statements, and where:

- loops have a constant step size;

- loops have bounds that are affine expressions of the enclosing loop iterators, static program parameters, and constants;

- if-statements have affine conditions in terms of the loop iterators, static program parameters, and constants;

- index expressions of array references are affine constructs of the enclosing loop iterators, static program parameters, and constants;

- data flow between statements in the loop is explicit, which prohibits that two statements that contain function calls communicate through shared variables invisible to the compiler.

An example of a static affine nested-loop program is shown in Figure 2.2.

```

#parameter 10 <= N <= 100;</pre>

2 for (i=0; i \le 2*N; i++)

for (j=0; j<= 4*N; j++)

3

a[i][j] = read_data ();

// statement S0

5 for (i=0; i \le N; i++) {

for (j=i; j<= N; j++) {

if (i+j \le N-1) {

a[i][j] = filter(a[2*i][4*j]); // statement S1

9

10

// statement S2

write_data(a[i][j]);

11

12 }

```

Figure 2.2: Example code of a SANLP

A static program parameter N is defined in line 1. This static parameter indicates that N can take a value between 10 and 100 which, however, cannot change at run-time. Using static parameters is very useful because an equivalent parallel specification, such as a PPN, needs to be derived only once, even if some requirements of the application change. Loops need not necessarily be perfect nests. That is, the program statements can appear at any level of the nested-loop, and thus not necessarily at the innermost loop level. Furthermore, the program statements can be guarded by if-statements, as shown in line 7. However, the conditions in these if-statements can only be affine combinations of loop iterators, static program parameters, and constants, and thus cannot have data dependent behavior. The functions in line 4, 8, 10 read and write data only through arrays, and not for example through shared variables, or pointers to the arrays not visible to the compiler. In other words, the data flow is made explicit by reading/writing data only through affine array accesses.

The polyhedral model is an appealing model to represent and manipulate loop nest structures and their program statements in static affine-nested loop programs, as shown in for example [69], [63], [70]. Program parts that can be modeled with the polyhedral model are called *static control parts* (*SCoPs*) in the compiler community [76]. To be more precise, a SCoP is defined as a single-entry-single-exit region of the control-flow where loops bounds and conditional predicates are affine functions enclosing loop counters and invariant parameters. Once the polyhedral model is extracted from a SANLP or SCoP, see Section 2.4, data dependence analysis and loop restructuring transformations such as loop fusion, loop fission and strip-mining can be efficiently implemented using existing tools (e.g., PolyLib [98], the Parma Polyhedral Library, and Cloog [7]). The reason is that the iteration domain of a program statement, i.e., all iterations of that statements, are represented by a single geometrical object - a polyhedron. This polyhedron can be analyzed with PILP techniques as presented in Section 2.2.

Although the polyhedral model does impose some restrictions on the input program, in many application domains it is natural to express time critical parts of the applications in the form of a SANLP. Examples are DSP and audio/video stream-based applications in consumer electronics, modeling and simulation applications in high performance computing, molecular biology, radio astronomy, medical imaging, and high energy physics. Therefore, the polyhedral model is highly relevant because it enables efficient code restructuring and analysis in many program code parts.

### 2.4 Extracting the Polyhedral Model from SANLPs

The polyhedral model is a description of all program statements and their iteration points in Static Affine Nested-Loop Programs (SANLPs) with polyhedra. We refer to all iteration points of a program statement as the iteration domain, which in the program code (i.e., the SANLP) is defined by the enclosing loops of the program statements. Since the iteration points of a program statement are executed in a particular order, the polyhedral objects that model these iterations are ordered as well, i.e., the polyhedral model that we use for our program analysis consist of:

- polyhedra that define the iteration domains of program statements,

- a lexicographical ordering (see Section 2.2) of the points within the polyhedra.

- and data access functions for array references, which map a point from the iteration domain to a point in the data space that is accessed by the array references, i.e., the affine index expression as discussed in Section 2.3.

In the polyhedral model that we extract from SANLPs, an iteration vector is associated with each program statement. The dimension of the vector is equal to the number of loops that enclose the statement. The i-th component of the vector corresponds to the value of a loop iterator at depth i. Thus, the iteration domain of a statement is given by a set of linear inequalities defining a polyhedron in an d-dimensional domain, where d corresponds to the dimension of the iteration vector, i.e., the depth of the enclosing loop nest. In fact, the polyhedral model of the iteration domain of a statement is just a set of linear equalities and inequalities. Here is an example.

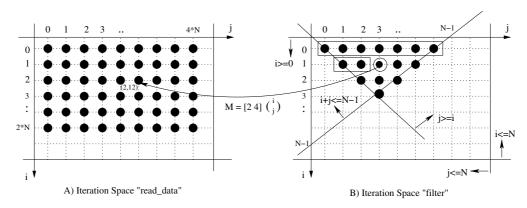

Figure 2.3: Iteration Space of read\_data and filter Function Call Statements

Figure 2.3 shows the two iteration domains of the read\_data and filter function call statements from Figure 2.2. Let us focus on the iteration domain of the

filter function call statement shown in Figure 2.3 B). For brevity, we refer to this statement as S1. Since statement S1 is enclosed by two for-loops i and j, its iteration domain is 2-dimensional, and is referred to as  $D_{S1}$ . The lower/upper bounds of the enclosing loops are the first constraints that we take into account when defining the iteration domain of S1. Loop i starts at 0 and has maximum value of N, which translates to the following 2 constraints:  $i \geq 0$  and  $i \leq N$ . Loop j has an initial value equal to i and has a maximum value of N, which translates to another two constraints:  $j \geq i$  and  $j \leq N$ . In addition to the constraints imposed by the lower/upper bounds of loops, the execution of program statement S1 is guarded by an if-statement, which imposes another restriction on the iteration domain, i.e, only iteration points smaller than  $i + j \leq N - 1$  are executed. Figure 2.3 B) shows 5 different lines in a 2-dimensional domain, which correspond to the 5 constraints imposed by the upper/lower bounds of the loops and the if-statement as we have described above. Thus, the constraints restrict the iterations points that are executed by S1, and the iteration points actually executed by S1 are denoted by the solid dots in Figure 2.3 B), i.e., they form a triangle. These iteration points are executed in the order from top to bottom and from left to right. We have extracted all constraints on the execution of S1 to define its iteration domain  $D_{S1}$  in the polytope representation:  $D_{S_1}(N) = \{(i,j) \in \mathbb{Z}^2 \mid 0 \le i \le N \land i \le j \le N \land i + j \le N - 1\}.$ All executions of program statement S1 are in this way represented with one geometrical object, i.e., a polytope. Once an iteration domain has been extracted for a statement, it can be efficiently further analyzed and transformed using polyhedral analysis and tools. For example, the number of integer points of an iteration domain can be counted [18], [96] which is useful for loop optimizations [20] and data cache analysis [19]. Another application is the (re)scheduling of iterations and subsequently the code generation of iteration domains [7].

### 2.5 Polyhedral Process Networks

Extracting the polyhedral model for SANLPs as discussed in Section 2.4, enables exact data-flow analysis of scalar and array references. This exact data flow analysis uses the PILP techniques as discussed in Section 2.2 and is the most fundamental step in deriving PPNs in a fully analytical way from SANLPs as described in [89, 90, 95]. For an in-depth discussion on the derivation of PPNs, the reader is referred to these works. In this section, we only discuss the different properties of PPNs, and show the corresponding PPN for the code example in Figure 2.2.

In the partitioning strategy of the pn compiler [95], one autonomous process with local control and memories is created for each program statement. Subsequently, the control for the FIFO communication is automatically derived. We refer to pro-

cess networks derived by the pn compiler as *polyhedral process networks* (PPNs). The reason is that they are functionally equivalent to Static Affine Nested Loop Programs (SANLPs), the processes are structured in a particular way, and the execution of processes and FIFO reads/writes are described by polyhedra. Polyhedral process networks are, therefore, a special case of Kahn Process Networks (KPNs) [40], because Kahn Process Networks is a simple, yet powerful model of computation that only specifies how processes synchronize and communicate. Thus, the KPN model of computation does *not* impose any restrictions on, for example, the internal structure of processes and only defines that processes use a blocking FIFO read primitive and have unbounded FIFO buffers. However, as already mentioned above, the processes in PPNs are internally structured in a particular way. That is, in each execution of a process, we can distinguish a *Read* phase (R), an *Execute* phase (E), and a *Write* phase (W). To be more specific, a process consists of:

- 1. a list of *input port domains* to read all the function input arguments from the corresponding input FIFO channels,

- 2. a *function* that processes the input arguments and produces function output arguments, and

- 3. a list of *output port domains* to write the function output arguments to the corresponding output FIFO channels.

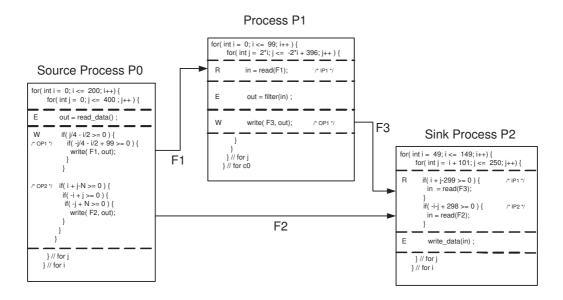

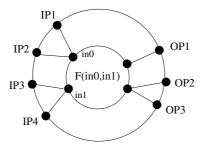

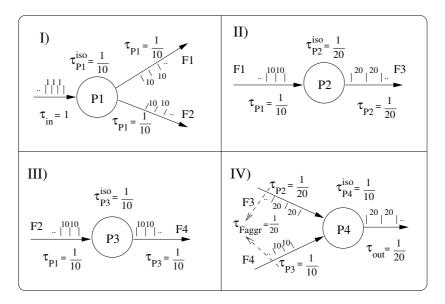

There can be two exceptions: *source* and *sink* processes. The former only generates data and does not read any data from other processes. The latter only collects data and does not write any data to other processes. However, source/sink processes can have incoming/outgoing channels, but then these channels are self-channels and data is read/written from/to itself. We illustrate the structure of the processes in a PPN with an example shown in Figure 2.4. This PPN is derived from the SANLP shown in Figure 2.2, where we have set the parameter N to 100. Since that SANLP consists of 3 statements S0, S1 and S2, the corresponding PPN consists of 3 processes P0, P1 and P2.

It can be seen that process  $P\theta$  is a source process because it does not read data from other processes, and that process P2 is a sink process because it does not write data to other processes. Process P1, on the other hand, first reads data from FIFO channel F1, processes it by executing function filter, and writes the result to its outgoing FIFO channel F3. Thus, it clearly shows the different read, execute, write phases as also indicated with the letters R, E, and W in Figure 2.4. Furthermore, we see that each process executes a particular function that corresponds to a function from the SANLP.

Figure 2.4: Derived Polyhedral Process Network (PPN) Model and its Representation in Executable Program Code

**Definition 3** A process function represents the computational part of a process. It corresponds to a function call statement in the sequential application that is a pure function without side-effects which only reads/writes through its input/output arguments.

For the PPN in Figure 2.4, the process function of  $P\theta$  is read\_data, and we see that filter and write\_data are the process functions of processes P1 and P2, respectively. These process functions are important for the process splitting and merging transformations that we present in Chapters 3 and 4, because the goal of both transformations is to create a more load-balanced PPN. Therefore, it is important to know the cost for executing the process function once, and we refer to this as the process workload.

**Definition 4** The process workload of a process  $P_i$ , denoted by  $W_{P_i}$ , represent the total number of required time units to execute the process function once, provided that i) all its input data is available (i.e., the reading phase is ignored), and ii) the time to write the output data is excluded (i.e., the writing phase is ignored).

To give an example for the PPN shown in Figure 2.4, one can think of the read\_data process function as a very light-weight process function that only reads data from a

memory location, i.e., the process workload  $W_{P0}$  is very small as executing that function is completed in a few clock cycles. The filter process function can be considered to be a more coarse-grain function as some actual computation is performed on the data. Thus, the process workload  $W_{P1}$  is much larger than  $W_{P0}$ . Similar to the read\_data function, the write\_data process workload  $W_{P2}$  is very small as only data is written back to some memory location and not any computations on the data is performed. The process workload does not include the time required to read/write the data before/after executing the process function.

**Definition 5** A process iteration of a process  $P_i$  is defined as a single execution of the process function, where first all input data is read from incoming FIFO channels (i.e., the read phase), the process function is executed (i.e., the execute phase), and subsequently all output data is written to outgoing FIFO channels (i.e., the write phase).

All iterations of a process are described by a process iteration domain.

**Definition 6** The process iteration domain of a process  $P_i$ , denoted by  $D_{P_i}$ , is defined as all process iterations of process  $P_i$  and is described by a set of equalities and inequalities, i.e., a polytope.

Thus, the process iteration domain is described with a polytope as we have discussed in Section 2.1. For process P1, for example, the process iteration domain is defined as  $D_{P1} = \{(i,j) \in \mathbb{Z}^2 \mid 0 \le i \le 99 \land 2i \le j \le -2i + 396\}$ . This corresponds to the control part, i.e., the two for-loops, of process P1 as can be seen in Figure 2.4.

**Definition 7** The process iteration domain size, denoted by  $|D_{P_i}|$ , represents the total number of iterations of process  $P_i$ .

The process iteration domain size is obtained by counting the number of integer points in a polytope, which is supported by the polyhedral library PolyLib [98] as also indicated in Section 2.2. Calculating a process iteration domain sizes, is obviously the first prerequisite to estimate the total execution time of a process. It is used to evaluate the process splitting transformation and is further discussed in Chapter 3.

Finally, we give 3 definitions that are related to the communication in polyhedral process networks. First, we consider input port domains that implement the control to read data from FIFO channels, then we define a mapping function that specifies an iteration point where data is produced, and finally we define an output port domain that specifies a set of points that generate data for a particular input port.

**Definition 8** The n-th input port domain of process  $P_i$ , denoted by  $IP_{P_i}^n$ , is defined as a subset of the process iteration domain where data is read from the n-th incoming FIFO channel, i.e.,  $IP_{P_i}^n \subseteq D_{P_i}$ .

28 Background

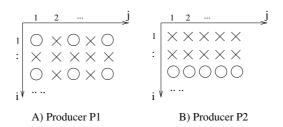

Consider process P1 in Figure 2.4, which has one input port domain  $IP_{P1}^1$ . This input port domain is read at each process iteration, which means that the input port domain contains the same points as the process iteration domain, i.e.,  $IP_{P1}^1 = D_{P1} = \{(i,j) \in \mathbb{Z}^2 \mid 0 \leq i \leq 99 \land 2i \leq j \leq -2i + 396\}$ . But when we look at process P2, for example, then we see that the input data is sometimes read from  $IP_{P2}^1$  and in other cases from  $IP_{P2}^2$ , i.e. they are a subset of the process iteration domain. To be more specific, we see that  $IP_{P2}^1 = \{(i,j) \in \mathbb{Z}^2 \mid i+j-299 \geq 0\} \cap D_{P2}$ , and that  $IP_{P2}^2 = \{(i,j) \in \mathbb{Z}^2 \mid -i+j+298 \geq 0\} \cap D_{P2}$ , where  $D_{P2} = \{(i,j) \in \mathbb{Z}^2 \mid 49 \leq i \leq 149 \land i+101 \leq j \leq 250\}$ . Note that these two input ports are mutually exclusive. The reason is that the write\_data process function has only one input argument and process P2 needs only one input token per process iteration from one of these two input ports.

In a similar way, we define an output port domain which represents the process iterations for which writing data to a particular FIFO channel occurs.

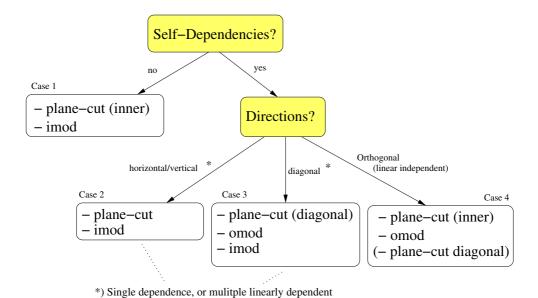

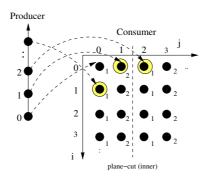

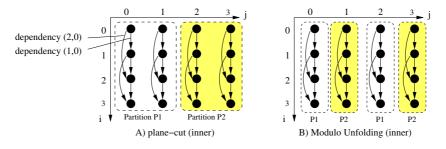

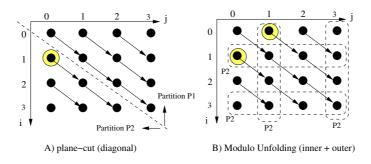

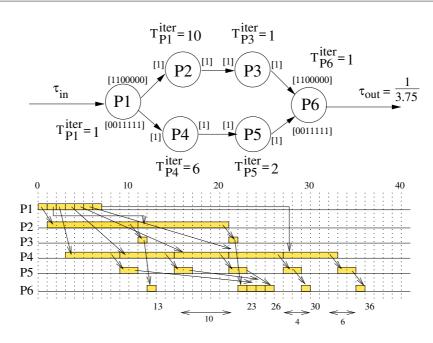

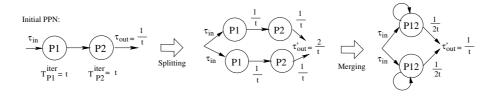

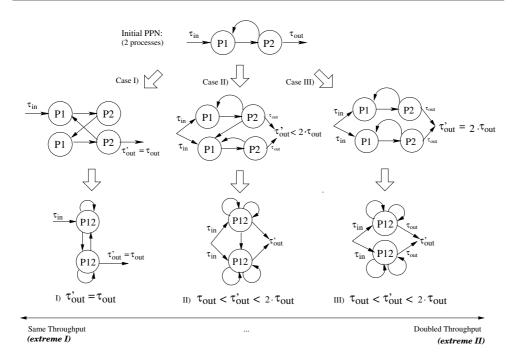

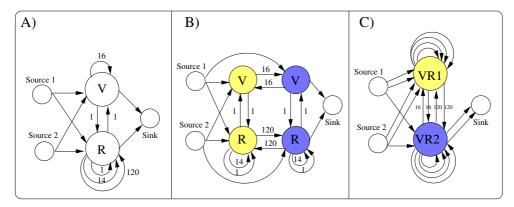

**Definition 9** The n-th output port domain of a process  $P_i$ , denote by  $OP_{P_k}^n$ , is defined as the subset where data is written to the n-th outgoing FIFO channel, i.e.,  $OP_{P_k}^n \subseteq D_{P_k}$ .