## **Design Project FDSD: November – December 2024**

Design, implement, and simulate a simple 4-bit processor using the Xilinx design tool and simulator. The processor executes the following instruction set:

| Instruction<br>Mnemonic | Operation             | Description                                                  |

|-------------------------|-----------------------|--------------------------------------------------------------|

| LDA #value              | $A \leftarrow value$  | Load register A with <i>value</i>                            |

| LDB #value              | B ← value             | Load register B with <i>value</i>                            |

| SHLA                    | A ← A << 1            | Shift-left with 1 bit the value of register A                |

| SHRA                    | $A \leftarrow A >> 1$ | Shift-right with 1 bit the value of register A               |

| MAB                     | B ← A                 | Move the value of reg. A to reg. B                           |

| ADDAB                   | $A \leftarrow A + B$  | Add reg. A to reg. B and store the result in reg. A          |

| NOTA                    | A ← A'                | Complement reg. A                                            |

| JC #value               | $PC \leftarrow value$ | Jump to address = <i>value</i> , <b>if carry flag is set</b> |

The top-level schematic of the processor is given in the **Appendix file "myProcessor.pdf"**. Use this architecture when you make your design. The processor consists of the following components:

- 1. Two general purpose 4-bit registers **register\_A** and **register\_B**;

- 2. One 4-bit Arithmetic and Logic Unit (**ALU**) that executes 4 operations:

- Addition: When S0 = 0 and S1 = 0 then res(3:0) ← A(3:0) + B(3:0);

- Shift-left: When S0 = 0 and S1 = 1 then res(3:0) ← (A(3:0) shifted-left with one bit);

- Shift-right: When S0 = 1 and S1 = 0 then res(3:0) ← (A(3:0) shifted-right with one bit);

- **Complement:** When **S0** = **1** and **S1** = **1** then **res(3:0)** ← **A(3:0)'**;

- 3. Two multiplexers 2-to-1 4-line MUXs MUX4\_2to1;

- 4. 1-bit Status Register stores the carry flag of the ALU after ADDAB instruction is executed.

- 5. One 4-bit **Program Counter (PC)** register that is used as an address generator for the program memory of the processor;

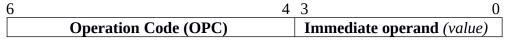

- 6. One program memory **ROM16x7** that has size 16 memory locations each 7 bits wide. In this memory the program is stored. Every instruction in the program occupies one memory location. The format of each instruction in the memory is as follows:

**OPC** is the code of the instruction. *value* is the operand that is used when instructions LDA, LDB, and JC are executed (see the instruction table above).

7. One **Instruction Decoder** component. It takes as an input an OPC and decodes the corresponding instruction. The outputs of the decoder are control signals that configure the data-path of the processor (register\_A, register\_B, the two MUX4\_2to1, Program Counter, Status Register, and ALU) in accordance with the instruction that has to be executed.

## **Project Schedule and Deliverables**

The project described above will be split and implemented in five small tasks.

1. **Task1:** Design, implementation, and simulation of components **MUX4\_2to1**, **register\_A**, and **register\_B**.

To be delivered **no later than 20.11.2024**;

- 2. **Task2:** Design, implementation, and simulation of components **ALU** and **Status Register.** To be delivered **no later than 27.11.2024;**

- 3. **Task3:** Design, implementation, and simulation of components **ROM16x7** and **Program Counter**. To be delivered **no later than 04.12.2024;**

- 4. **Task4:** Design, implementation, and simulation of component **Instruction Decoder**. To be delivered **no later than 11.12.2024;**

- 5. **Task5:** Connect all components designed in Tasks 1 to 4 in order to build the simple processor. Write **one small program** that computes the **absolute value** of the expression |X/2 Y|. The result has to be in **register B**. The operation "/" is integer division. When the program is written run it 2 times. First, load the program in the memory with X = 5 and Y = 11. Second, load **the same program** with X = 13 and Y = 4. The simulations should show that your processor works correctly. To be delivered **no later than 31.12.2024**.

**NOTE1:** You have to work on the project tasks in a group of max 2 students! So, make sure that you find a partner to work with and you should not change your partner throughout the project.

<u>NOTE2</u>: When you design your specific processor components, you are allowed to (re-)use all predesigned components that you can find in the Xilinx project library! So, study all components that are available in the library and try to use them as much as possible in order to save your time and effort.

**NOTE3:** You have to deliver each task in electronic form **by e-mail to the assistants at** "dite.liacs@gmail.com". To do this you have to automatically cleanup (ask the assistants how) and zip the whole Xilinx project in which you do and simulate the tasks. After you zip the project try to unzip it on another computer in rooms DM.0.09-PC, DM.0.13-PC, DM.0.17-PC, or DM.0.21-PC and to run it in order to check if you have included all needed files. If sending the zip file via e-mail fails because of SPAM filters, etc., then upload the zip file on GoogleDrive and send us a link to the zip file such that we can download it. Make the link accessible to everyone and keep the link with each zip file active/available at least 90 days after you send it to us!

**IMPORTANT:** If we cannot run and simulate the project, you have sent, we will assume that you have not completed your task. So, be careful to send us a working/correct project (including all needed testbench files) such that we can properly run, simulate, and test/check your project using your testbench files.

Together with each zip file you have to send us a separate text file/report (max 2 pages) explaining what you did and how to run and simulate the project that is in the zip file. The text file/report is important and its quality will be graded as well in terms of clarity, completeness of explanation, etc.

**NOTE4**: It is very beneficial for you to attend the **on-campus Design Project hands-on classes every Wednesday from 15:15h to 17:00h in all computer rooms DM.0.09-PC to DM.0.21-PC**. There, you can do parts of the project together with us, you can ask questions, and you will receive help from us related to the tasks above. **However, if needed, you have to spend sufficient amount of extra time on the project in the computer rooms or at home in order to complete it successfully!**

## **Grading of Your Project**

- To receive grade 6.0 you have to *complete successfully* Task1, Task2, Task3, and Task4;

- Receiving a grade higher than 6.0 will depend on how you perform Task5;

## **IMPORTANT: Completing a task successfully means:**

- 1. You have delivered the task on time according to the schedule above. If you fail to do this we will assume that you have not completed your task. **So, take the schedule seriously!**

- 2. The delivered task contains working/correct Xilinx implementation together with the testbench files you have used for the simulation of your implementation.

- 3. You have delivered a text file/report that explains what you have done in the task and how to simulate your implementation.